## Radiofrequency power amplifiers in horizontal current bipolar transistor technology

Osrečki, Željko

**Doctoral thesis / Disertacija**

2021

Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Faculty of Electrical Engineering and Computing / Sveučilište u Zagrebu, Fakultet elektrotehnike i računarstva

Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:168:451203

Rights / Prava: In copyright/Zaštićeno autorskim pravom.

Download date / Datum preuzimanja: 2024-05-15

Repository / Repozitorij:

FER Repository - University of Zagreb Faculty of Electrical Engineering and Computing repozitory

#### FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Željko Osrečki

# RADIOFREQUENCY POWER AMPLIFIERS IN HORIZONTAL CURRENT BIPOLAR TRANSISTOR TECHNOLOGY

**DOCTORAL THESIS**

#### FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

## Željko Osrečki

# RADIOFREQUENCY POWER AMPLIFIERS IN HORIZONTAL CURRENT BIPOLAR TRANSISTOR TECHNOLOGY

**DOCTORAL THESIS**

Supervisor: Professor Tomislav Suligoj, PhD

### FAKULTET ELEKTROTEHNIKE I RAČUNARSTVA

Željko Osrečki

## RADIOFREKVENCIJSKA POJAČALA SNAGE U TEHNOLOGIJI BIPOLARNOGA TRANZISTORA S HORIZONTALNIM TOKOM STRUJE

**DOKTORSKI RAD**

Mentor: Prof. dr. sc. Tomislav Suligoj

Zagreb, 2021.

| This thesis was done at the University of Zagreb, Faculty of Electrical Engineering and |

|-----------------------------------------------------------------------------------------|

| Computing, Department of Electronics, Microelectronics, Computer and Intelligent Sys-   |

| tems.                                                                                   |

|                                                                                         |

| Supervisor: Professor Tomislav Suligoj, PhD                                             |

| Dissertation has 156 pages                                                              |

|                                                                                         |

| Dissertation no.:                                                                       |

Tomislav Suligoj received Diploma engineer, M.Sc. and Ph.D. degrees in electrical engineering from the University of Zagreb, Faculty of Electrical Engineering and Computing (FER), Croatia, in 1995, 1998 and 2001, respectively. Currently, he is a full professor at FER, Department of Electronics, Microelectronics, Computing and Intelligent Systems, teaching the courses in the area of electronics and microelectronics. He was a visiting researcher at the University of California, Los Angeles (1999-2001) and a postdoctoral researcher at the Hong Kong University of Science and Technology (2001-2002). He has been a Principal Investigator of more than 20 projects so far supported by the government agencies, international companies and universities. He published more than 20 patents and more than 150 papers in journals and conference proceedings in the area of design, measurements and modelling of electron devices, microand nano- electronics, semiconductor technology and integrated circuit design. Prof. Suligoj received 14 scientific awards including National Science Award in 2015; Golden plaque at innovation exhibition ARCA; Best paper awards at MIPRO MEET conference, Faculty medals "Josip Lončar" for outstanding Doctoral Dissertation, and Fulbright scholarship. He is a Technical Program Committee member, Publications co-chair and a Chairman of Device Physics Subcommittee at IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM) He is a Steering Committee member of MIPRO MEET conference. He was a President of Electron Devices / Solid-State Circuits Joint Chapter, IEEE Croatia Section from 2010 until 2013. He gave numerous invited talks at the conferences, universities, institutions and companies.

Tomislav Suligoj je diplomirao, magistrirao i doktorirao u polju elektrotehnike na Sveučilištu u Zagrebu, Fakultetu elektrotehnike i računarstva (FER), 1995., 1998. odnosno 2001. godine. Trenutno je redoviti profesor na Zavodu za elektroniku, mikroelektroniku, računalne i inteligentne sustave FER-a gdje predaje kolegije u području elektronike i mikroelektronike. Bio je gostujući istraživač na University of California, Los Angeles od 1999. do 2001. godine te na poslijedoktorskom usavršavanju na Hong Kong University of Science and Technology od 2001. do 2002. Dosada je vodio više od 20 projekata financiranih državnih institucija, međunarodnih kompanija i Sveučilišta. Objavio je više od 20 patenata i više od 150 radova u časopisima i zbornicima konferencija u području projektiranja, mjerenja i modeliranja elektroničkih elemenata, mikro- i nano- elektronike, poluvodičke tehnologije i projektiranja integriranih sklopova. Prof. Suligoj dobitnik je 14 nagrada uključujući Državnu nagradu za znanost 2015. g., Zlatnu plaketu na izložbi inovacija ARCA, Best paper award na MIPRO MEET konferenciji, srebrnu plaketu "Josip Lončar" za posebno istaknutu doktorsku disertaciju te Fulbright-ovu stipendije. Član je Technical Program Committee, Publications co-chair i Chairman of Device Physics Subcommittee konferencije IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM). Član je Steering Committee konferencije MIPRO MEET. Bio je predsjednik Odjela za elektroničke elemente i poluvodičke integrirane sklopove Hrvatske sekcije IEEE 2010.- 2013. Održao je velik broj pozvanih predavanja na međunarodnim konferencijama, sveučilištima, institutima i kompanijama.

#### **Abstract**

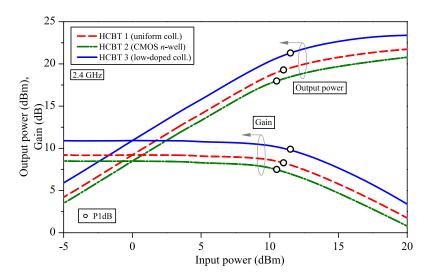

The large-signal performance of the horizontal current bipolar transistor (HCBT) is investigated by extensive measurements and simulations, and its suitability for the radiofrequency power amplifier design is demonstrated by designing advanced high-efficiency and wideband power amplifiers. An accurate and calibrated scalar load-pull setup is firstly employed for the determination of the optimal input and output matching impedances for different HCBT structures to achieve the maximum output power. The HCBT in Class-AB regime at the fundamental frequency of 2.4 GHz provides up to 25 dBm output power with the gain of 11 dB, exhibiting optimal matching impedances close to 50  $\Omega$ . The suitability of different collector region designs is investigated by performing load-pull measurements for the HCBTs with uniform, n-well, and low-doped collectors, where the low-doped HCBT achieves the highest gain, whereas the nwell HCBT provides the highest collector efficiency in the power back-off power range. Due to its robustness in large-signal operation, the HCBT is analyzed in the regime where the load line penetrates the impact ionization region, for the base-emitter bias applied by either a voltage or current source. Additionally, the boundary of linear operation is found for the HCBT by developing a dedicated vector load-pull setup with the possibility of a time-domain waveform measurement in large-signal operation. A high-efficiency Doherty power amplifier is designed using discrete HCBTs at 2.4 GHz, where the amplifier achieves 38.7% collector efficiency with the modulated excitation of 3.5-dB peak to average power ratio. Finally, a wideband balanced amplifier with 700-MHz bandwidth at 2.4 GHz is designed, exhibiting efficiency greater than 35.6% over the bandwidth. The amplifiers provide a performance surpassing that of the most advanced power amplifiers implemented in costlier semiconductor technologies.

**Keywords**: horizontal current bipolar transistor (HCBT), bipolar transistors, large-signal, scalar load-pull, vector load-pull, waveform measurement, linear operating area, power amplifiers, Doherty, balanced.

## Radiofrekvencijska pojačala snage u tehnologiji bipolarnoga tranzistora s horizontalnim tokom struje

Ubrzani rast industrije mobilnih bežičnih komunikacija donosi sve veće brzine prijenosa podataka i proširenje područja primjene bežičnih komunikacija, s ciljem povećanja kvalitete i pouzdanosti komunikacije s bilo kojeg mjesta i u bilo koje vrijeme. Ovaj rast omogućava sklopovlje ekstremnih performansi sa mogućnosti rada na frekvencijama i do nekoliko teraherca. S obzirom da se od sklopovlja bežičnih komunikacija iz generacije u generaciju zahtijeva ogroman rast performansi, tako raste i cijena radiofrekvencijskih (RF) sklopova odgovornih za odašiljanje radiofrekvencijskog signala. Razne poluvodičke tehnologije koriste se za implementaciju ovih sklopova, poput III-V poluvodiča, što uzrokuje rast cijene implementacije u odnosu na CMOS tehnologije, koje se uobičajeno koriste u području digitalne i analogne elektronike. Cilj modernih bežičnih komunikacija su visoke performanse uz nisku potrošnju i, naravno, uz nisku cijenu implementacije. Doktorski rad pod naslovom "Radiofreguency power amplifiers in horizontal current bipolar transistor technology" (Radiofrekvencijska pojačala snage u tehnologiji bipolarnoga tranzistora s horizontalnim tokom struje), predstavlja tehnologiju bipolarnoga tranzistora s horizontalnim tokom struje (HCBT) kao idealnu tehnologiju za implementaciju RF pojačala snage u frekvencijskom području do 6 GHz, uz neznatno višu cijenu u odnosu na komercijalne CMOS procese. Cilj rada je istražiti i demonstrirati složena pojačala snage za bežične komunikacije visokih performansi i niske cijene, koja zadovoljavaju zahtjeve modernih bežičnih komunikacijskih standarda.

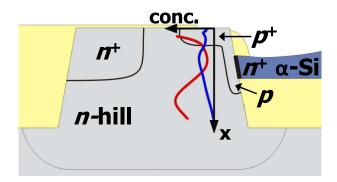

Prvo poglavlje "Introduction" daje osvrt na postojeća rješenja i donosi pregled najvažnije teorije bitne za razumijevanje u radu dobivenih rezultata. U prvom dijelu uvodnog poglavlja, dan je pregled najvažnijih bežičnih komunikacijskih standarda, počevši od prve generacije pa sve do pete generacije, čija implementacija je još u tijeku. Tendencija rasta frekvencije nosioca u modernih standarda, opravdana je povećanjem frekvencijskog pojasa modernih moduliranih signala, što omogućava ogroman rast brzine prijenosa podataka. Ovaj rast, nadalje, uzrokuje i rast složenosti radiofrekvencijskog predajnika, čije performanse uvelike određuju performanse cijelog komunikacijskog kanala. Opisana je osnovna arhitektura modernih RF predajnika, a glavne značajke moduliranih signala, kao rezultata rada predajnika, objašnjene su korištenjem simulacija Wi-Fi predajnika na 2.4 GHz. Modulacije, poput frekvencijskog multipleksa ortogonalnih podnosioca (OFDM), prikazane su pomoću konstelacijskih dijagrama, na kojima se promatra i utjecaj nelinearnosti komunikacijskog kanala na poslani, odnosno, primljeni signal. Glavni uzrok nelinearnosti u kanalu najčešće je RF pojačalo snage, čija je glavna uloga pojačati signal uz što manje izobličenje, i uz što nižu potrošnju energije. Blok shema pojačala snage objašnjena je korištenjem analize sklopova pomoću raspršnih parametara u režimu malog signala, a pomoću nelinearnog modela u režimu velikog signala. Glavni pokazatelji performansi pojačala snage, poput korisnosti, izlazne snage, pojačanja, i linearnosti, objašnjene su i matematički opisane kako stoji u standardima modernih bežičnih komunikacija. Nadalje, dan je pregled glavnih svojstava RF pojačala snage, poput klasa A, AB, i B, koje predstavljaju osnovni način povećanja korisnosti pojačala. U kontekstu optimizacije rada pojačala snage, dan je opis empirijskog načina utvrđivanja optimalnih radnih uvjeta koristeći mjerni sustav za karakterizaciju tranzistora u režimu velikog signala (eng. load-pull). Povećanje korisnosti pojačala snage dobiva se korištenjem naprednih arhitektura, poput Doherty i ET (eng. Envelope Tracking), čiji je rad i utjecaj na predani RF signal ukratko opisan u nastavku uvodnog poglavlja. Također, povećanje frekvencijskog pojasa, i time brzine prijenosa podataka, moguće je dobiti korištenjem arhitektura pojačala snage koje za glavnu zadaću imaju optimalni rad na širokom frekvencijskom pojasu, poput balanced RF pojačala snage. Povećanje korisnosti i frekvencijskog pojasa, može se dobiti i upotrebom naprednih poluvodičkih tehnologija, gdje su performanse sklopova projektiranih u tim tehnologijama ukratko opisane u nastavku. Na kraju poglavlja, opisana je tehnologija bipolarnoga tranzistora s horizontalnim tokom struje (HCBT), gdje je dan pregled najvažnijih mjerenih rezultata i varijanti tranzistora za postizanje visokih probojnih napona.

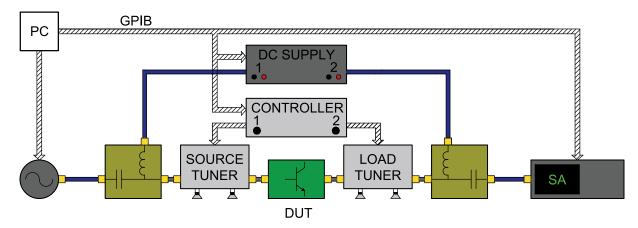

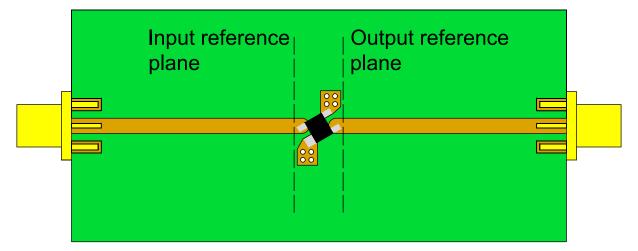

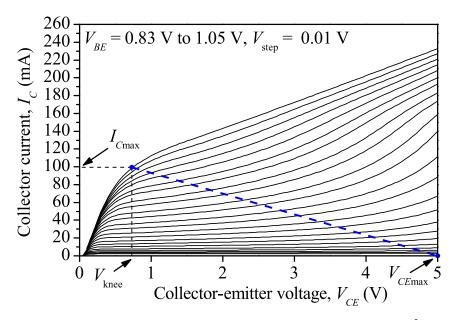

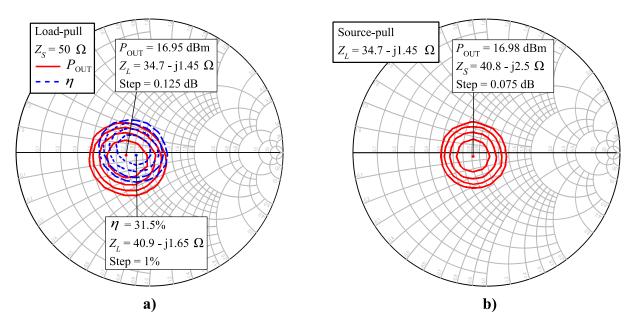

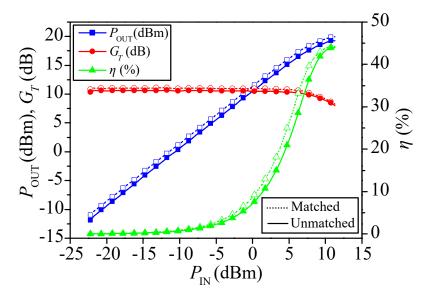

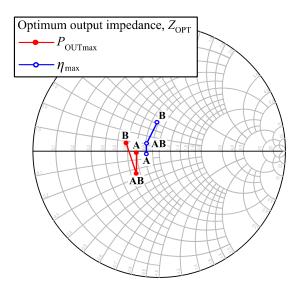

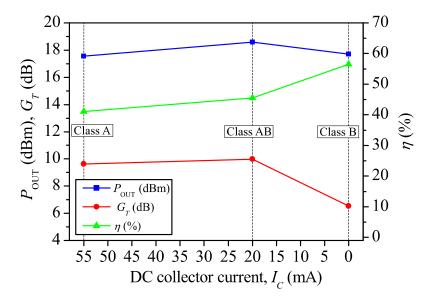

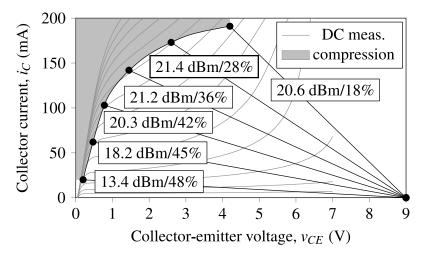

Drugo poglavlje opisuje skalarni mjerni sustav za karakterizaciju tranzistora u režimu velikog signala, metodologiju, i najvažnije rezultate koji se odnose na optimalne radne uvjete za HCBT u režimu velikog signala. Nadalje, opisana je korištena ispitna tiskana pločica za mjerenje diskretnih tranzistora, i prikazan je postupak uklanjanja utjecaja prijenosnih linija koje ostvaruju prijelaz sa koaksijalnog standarda mjerne opreme, na miktotrakastu liniju koja predstavlja sučelje sa mjerenim tranzistorom. Prvi mjerni rezultati predstavljaju performanse HCBT-a površine emitera od 31.2  $\mu$ m<sup>2</sup> uz zaključenje optimalnim impedancijama za postizanje maksimalne izlazne snage. Mjerene veličine, poput izlazne snage, pojačanja, i korisnosti, matematički su opisane, kao i analitička metoda za izbor početne istosmjerne radne točke za karakterizaciju. Metodologija mjerenja sadrži karakterizaciju tranzistora u režimu velikog signala uz zaključenje na ulazu i izlazu impedancijom od 50  $\Omega$ , mjerenje izlazne snage i korisnosti u ovisnosti o raznim vrijednostima ulazne i izlazne impedancije, i na kraju, mjerenje izlazne snage i korisnosti za optimalno zaključenje dobiveno iz prethodnih koraka analize. Uz optimalno zaključenje i rad u klasi A, HCBT postiže maksimalnu linearnu izlaznu snagu od 16.95 dBm i korisnost od 30%. Od tri analizirane klase rada, A, AB, i B, HCBT postiže najbolje performanse u klasi AB, gdje dostiže izlazu snagu od 18.6 dBm, pojačanje od 10 dB, i korisnost od 46%, uz optimalne impedancije bliske impedanciji sustava od 50 Ω. Rezultati ukazuju na pogodnost analiziranih HCBT-a za primjene u širokopojasnim RF pojačalima snage.

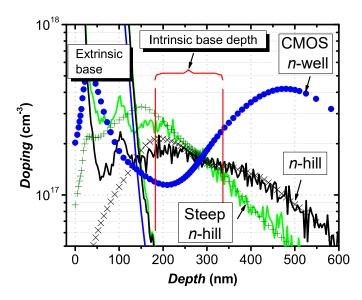

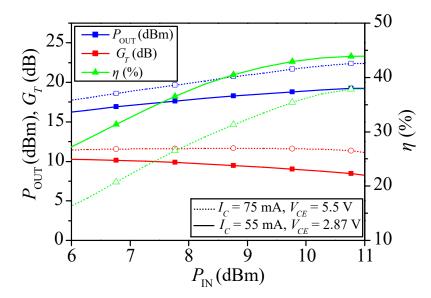

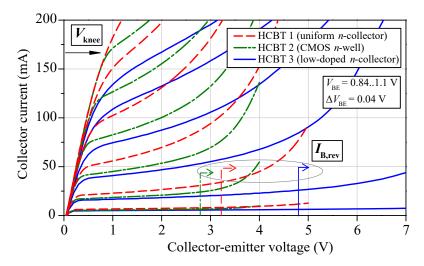

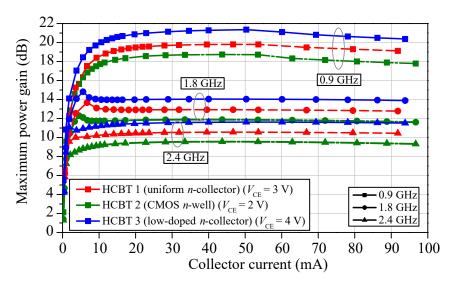

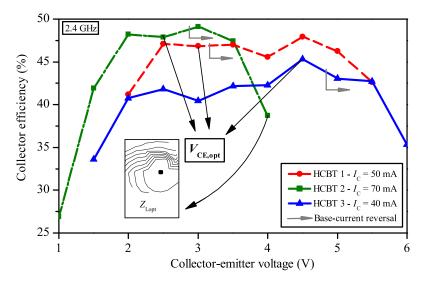

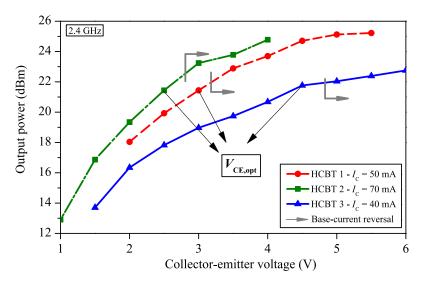

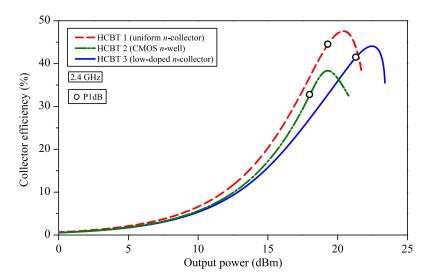

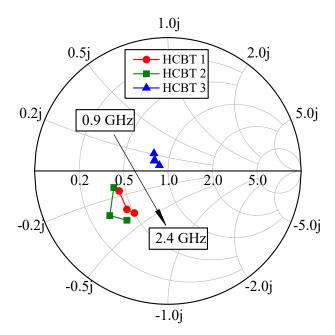

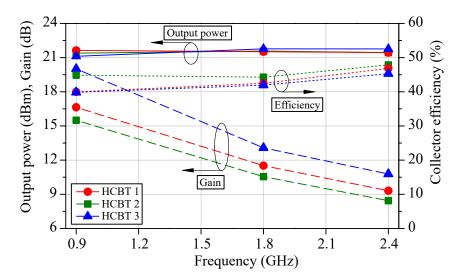

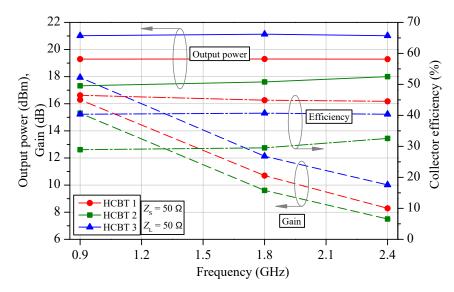

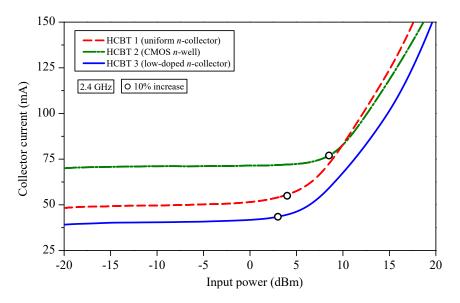

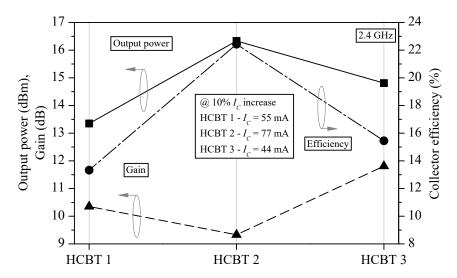

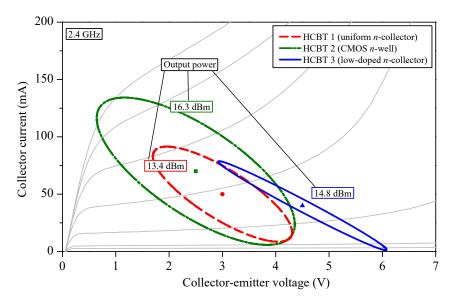

Utjecaj karakteristika strukture tranzistora na performanse u režimu velikog signala je, nadalje, ispitan karakterizacijom HCBT-a tri različita kolektorska doping profila, korištenjem sustava za karakterizaciju u režimu velikog signala. Tri tranzistora razlikuju se u maksimal-

nom dopingu, kao i u profilu primjesa u području intrinzičnog kolektora, a to su: HCBT sa uniformnim, CMOS n-well, i niskodopiranim kolektorom, a površine kolektora 58.5  $\mu$ m². Objašnjena je metodologija za izbor optimalne struje istosmjerne radne točke analizirajući maksimalno pojačanje snage za mali signal, na frekvencijama 0.9, 1.8, i 2.4 GHz. Izbor optimalnog napona istosmjerne radne točke temelji se na maksimalnom naponu između kolektora i emitera koji osigurava stabilan rad za sve vrijednosti snage ulaznog signala. Ovaj napon je, stoga, određen kao nešto niži napon od probojnog napona BV<sub>CEO</sub>. Mjerni rezultati pokazuju da HCBT sa niskodopiranim kolektorom postiže najviše pojačanje snage, a HCBT sa CMOS n-well kolektorom, najvišu korisnost, uz optimalno zaključenje na ulazu i izlazu. Također, HCBT sa niskodopiranim kolektorom ima optimalne impedancije najbliže 50  $\Omega$ , što pruža najbolje rješenje za primjene u širokopojasnim pojačalima snage. U području nižih ulaznih snaga od maksimalne (eng. power back-off), HCBT sa CMOS n-well daje najvišu linearnu izlaznu snagu i korisnost, pa tako predstavlja najbolji izbor u primjenama gdje je korisnost u linearnom području najvažniji parametar.

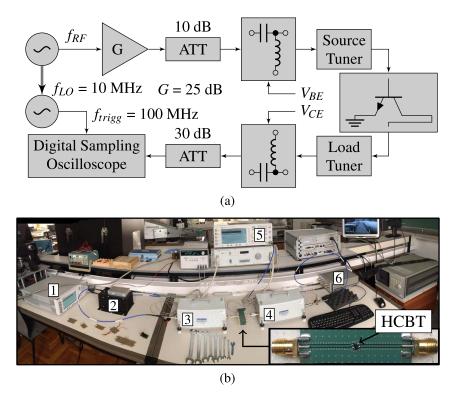

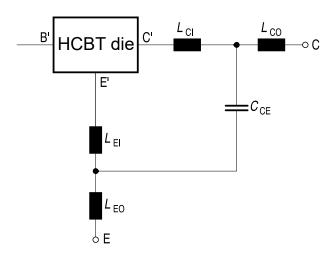

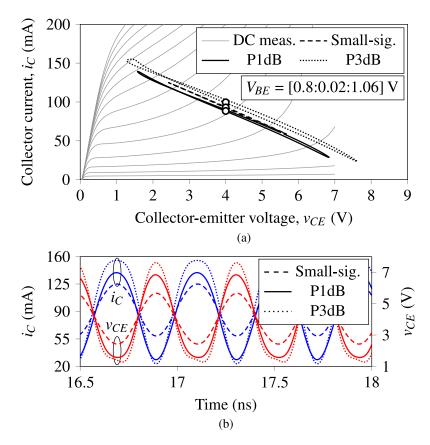

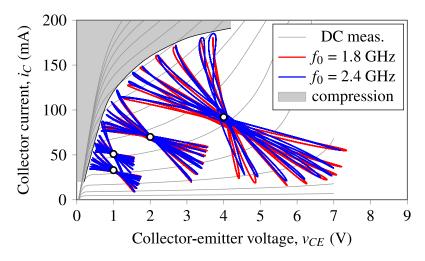

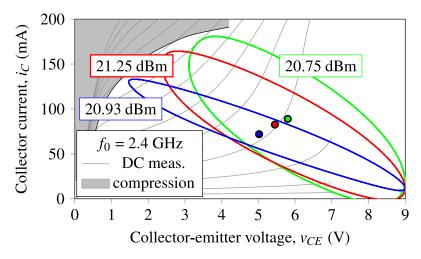

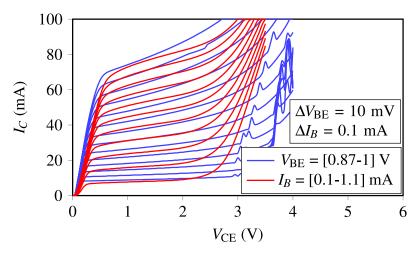

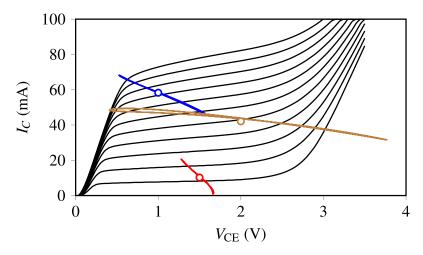

U trećem poglavlju, istražene su granice linearnog rada HCBT-a u režimu velikog signala. S ciljem pronalaska linearnog područja rada na visokim frekvencijama, postavljen je i kalibriran vektorski mjerni sustav sa mogućnosti mjerenja vremenskih valnih oblika na visokim frekvencijama. Navedeni mjerni sustav koristi osciloskop koji radi na principu poduzorkovanja za mjerenje periodičnih visokofrekvencijskih signala, a preciznom karakterizacijom komponenti sustava, mjerna referentna ravnina pomaknuta je na kolektorski kontakt na čipu unutar kućišta diskretnog tranzistora. Predstavljena je i opisana metodologija za mjerenje područja linearnog rada, koja obuhvaća snimanje radnih pravaca na frekvencijama 0.9, 1.8, i 2.4 GHz, za ulaznu snagu u kojoj pojačanje tranzistora padne za 1 dB (P1dB). Izborom odgovarajuće istosmjerne radne točke i impedancije tereta, određena je granica linearnog rada, koja je, nadalje, određena područjima zasićenja i Kirk efekta. Izmjerena granica definira istosmjernu radnu točku i radni pravac za maksimalnu izlaznu snagu, uz uvjet da je postavljen maksimalni izlazni napon tranzistora. Za niskodopirani HCBT, ova analiza daje maksimalnu izlaznu snagu od 21.25 dBm i korisnost od 30% u klasi A, uz maksimalni izlazni napon od 9 V.

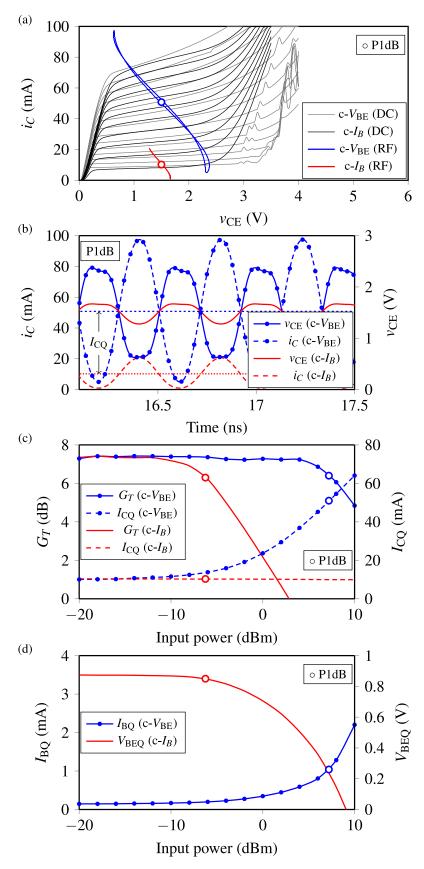

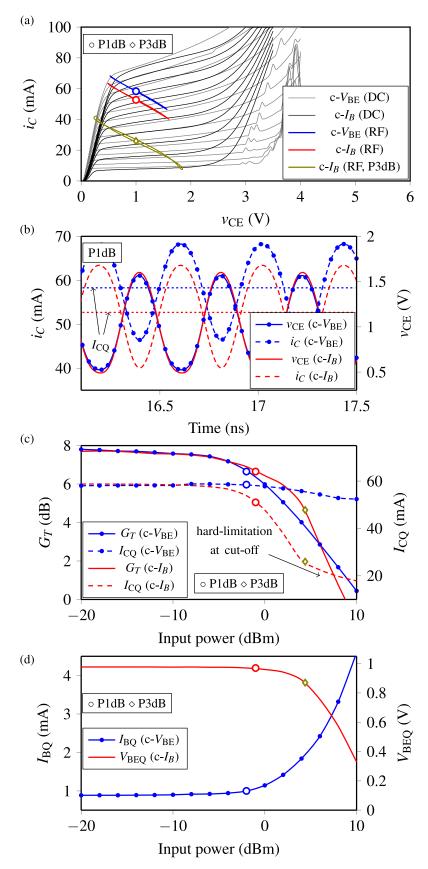

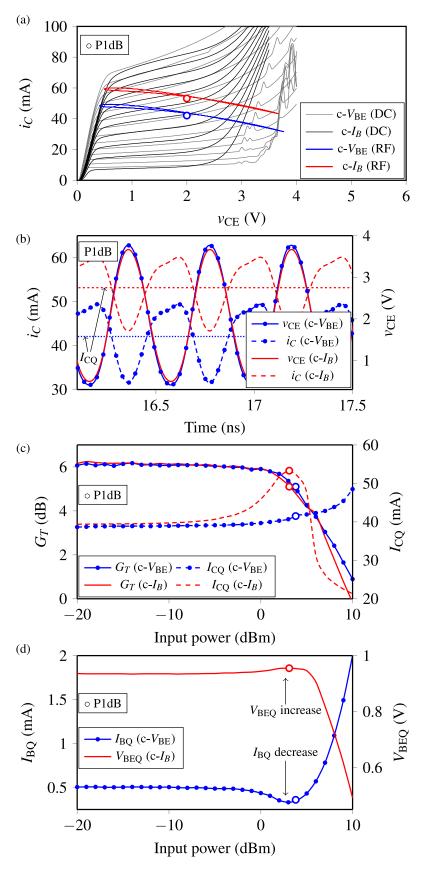

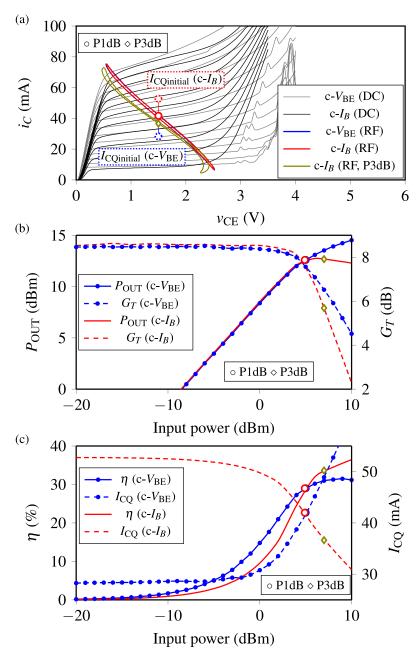

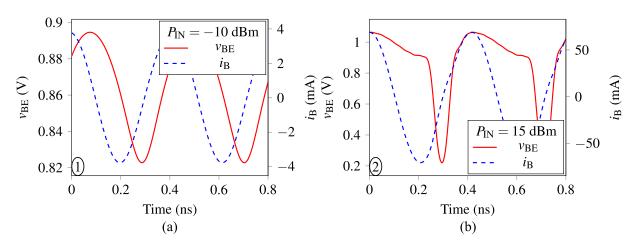

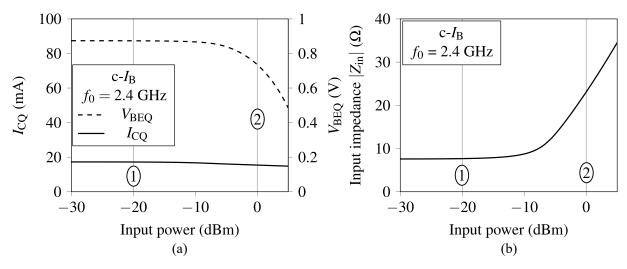

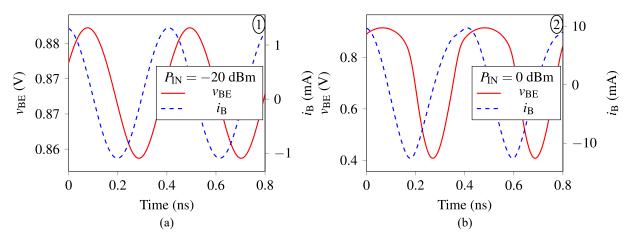

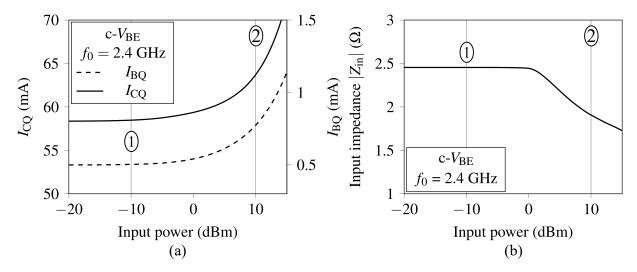

Drugi dio trećeg poglavlja predstavlja rezultate analize ponašanja istosmjerne radne točke u ovisnosti ulaznoj snazi. Točnije, analizirana je ovisnost istosmjernih veličina HCBT-a o ulaznoj snazi, i to za nelinearnost valnih oblika uzrokovanu različitim područjima izlaznih karakteristika bipolarnog tranzistora; zapiranjem, zasićenjem, i probojem. Glavne poteškoće u radu pojačala snage uzrokuje promjena istosmjerne točke prilikom ulaska u kompresiju, stoga, analizirani su radni pravci u točki kompresije, i to za dvije različite konfiguracije napajanja baznog kruga; naponskim i strujnim izvorom. Za izobličenje radnog pravca u zapiranju, rezultati pokazuju da je područje linearnog rada 13 dB veće za napajanje baznog kruga naponskim izvorom u odnosu na strujni izvor, što je rezultat rasta istosmjerne struje kolektora zbog izobličenja u

ulaznom krugu tranzistora. Suprotno je dobiveno za izobličenje u području zasićenja, gdje je područje linearnog rada 1 dB veće u slučaju napajanja baznog kruga strujnim izvorom. Zanimljivi rezultati dobiveni su za naponski hod veći od probojnog napona, gdje se utjecaj lavinske multiplikacije ne vidi na valnim oblicima struje i napona, ali je izražen kao nagli rast istosmjerne struje kolektora u blizini točke kompresije. Rezultati dobiveni u ovom poglavlju važni su za izbor optimalnih radnih uvjeta HCBT-a koji se koristi za projektiranje RF pojačala snage opisanih u sljedećim poglavljima.

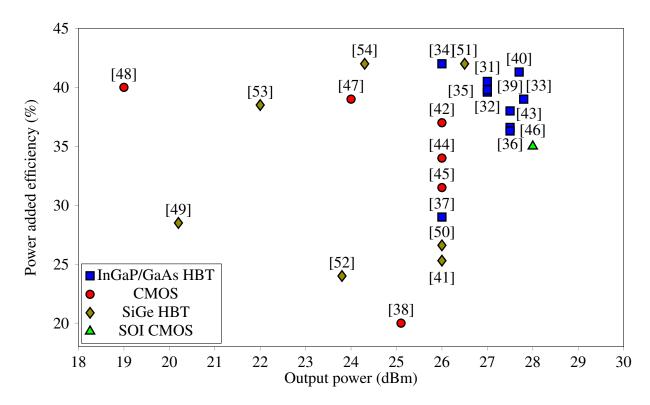

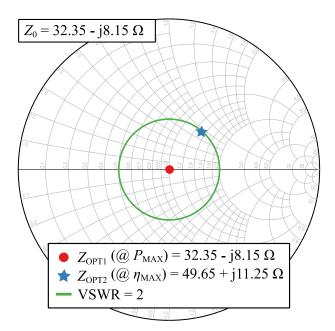

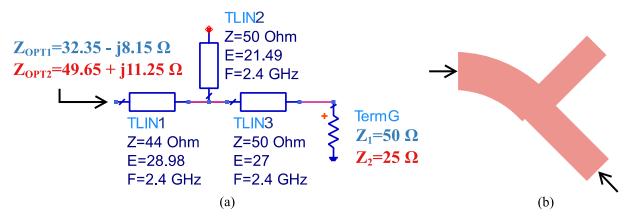

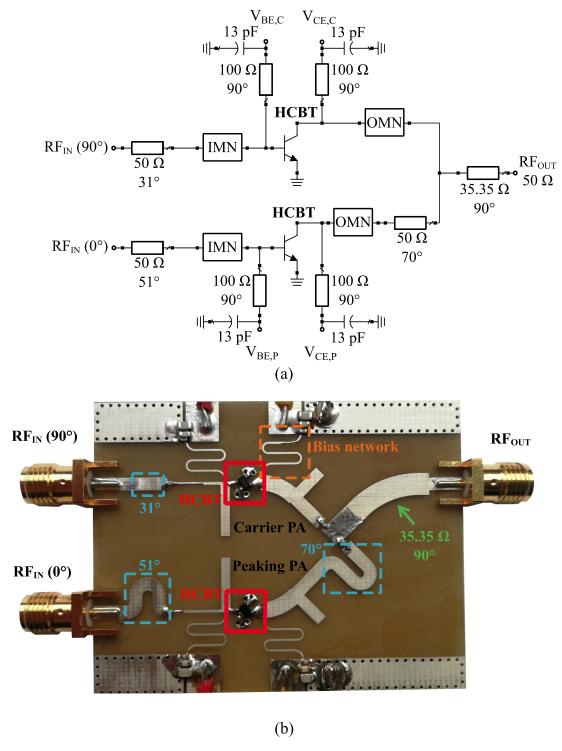

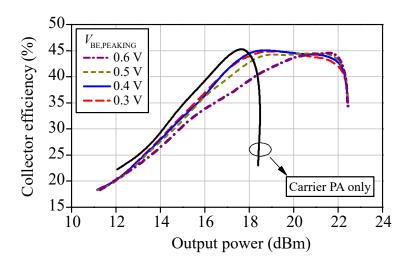

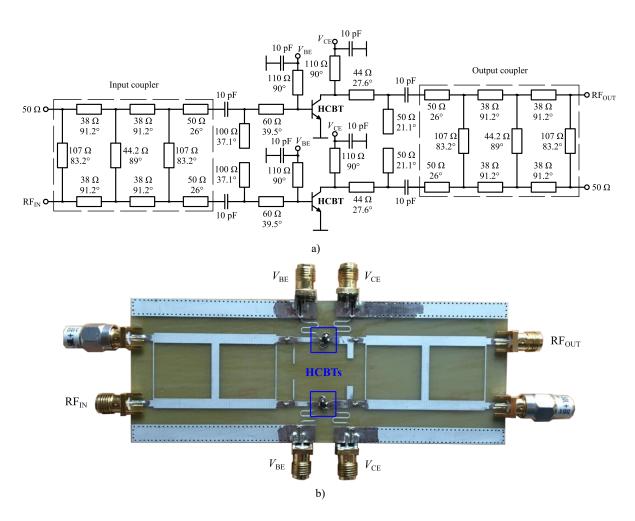

U četvrtom poglavlju, opisan je postupak projektiranja i karakterizacije Doherty RF pojačala snage izrađenog sa HCBT-om na 2.4 GHz. Ukratko je objašnjena teorija pojačala, gdje se koristi aktivna modulacija impedancije tereta pojačala za postizanje optimalnog prilagođenja i za snage ulaznog signala niže od snage u točki kompresije. Pojačalo se sastoji od dva jednostavnija pojačala snage, klase AB i C, gdje pojačalo klase C modulira izlaznu impedanciju pojačala klase AB. Optimalne impedancije za oba pojačala pronađene su korištenjem sustava za karakterizaciju tranzistora u režimu velikog signala, a ulazne i izlazne prilagodne mreže projektirane su koristeći elektromagnetske simulacije fizičkog dizajna pločice. Pojačalo je implementirano na pločici materijala FR4, dielektrične konstante 4.3, i debljine 1 mm, a prijenosne linije su mikrotrakastoga tipa. Doherty pojačalo implementirano s HCBT-ima postiže 22 dBm izlazne snage i maksimalnu korisnost kolektora od 45%. Uz pobudu moduliranim signalom treće generacije, omjera vršne i srednje snage (PAPR) 3.5 dB i širine pojasa od 10 MHz, pojačalo postiže 38.7% srednju korisnost kolektora, na frekvenciji nosioca od 2.4 GHz, što je usporedivo sa pojačalima implementiranim u naprednijim i skupljim poluvodičkim tehnologijama.

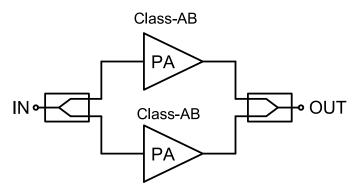

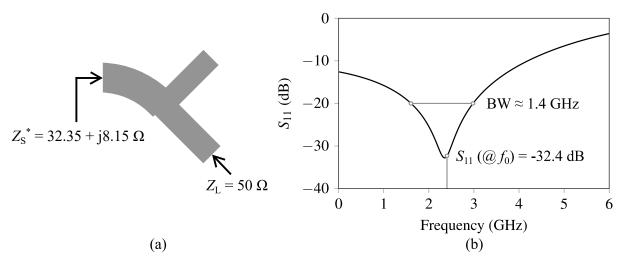

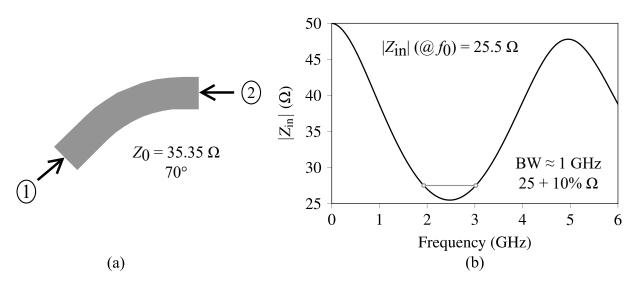

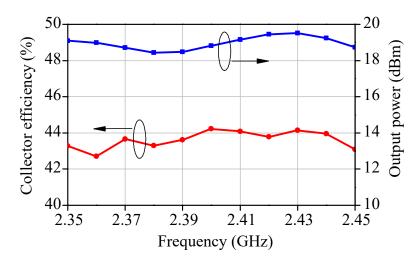

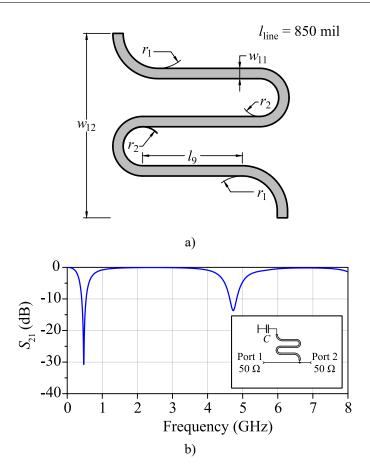

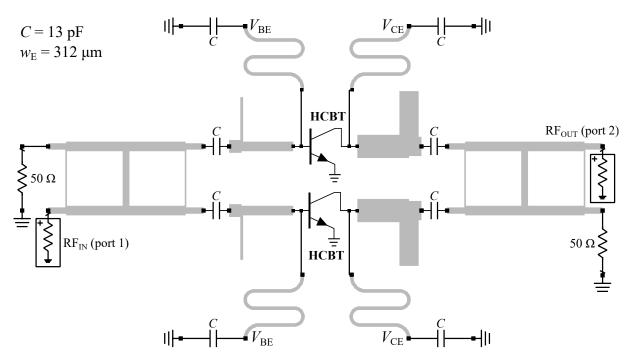

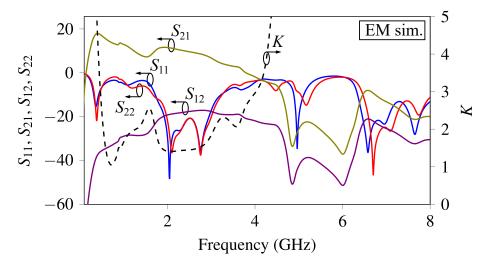

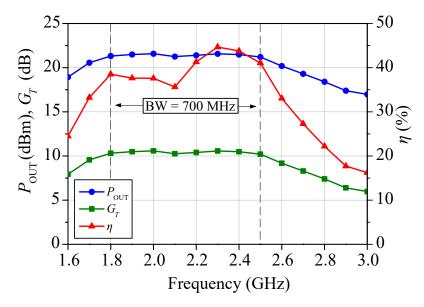

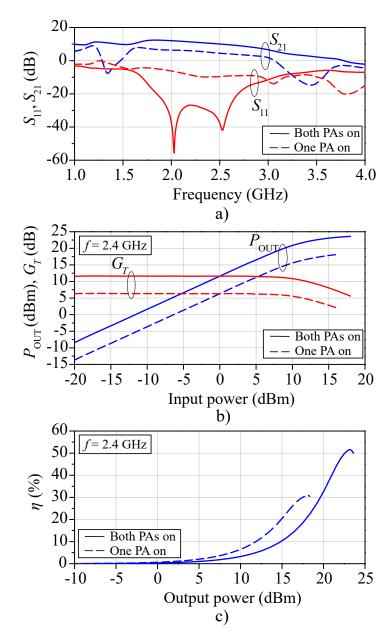

U petom poglavlju, opisano je projektiranje pojačala snage širokog pojasa tipa balanced, koje se sastoji od dva jednaka pojačala snage klase AB, a također je implementirano koristeći diskretni HCBT na središnjoj frekvenciji od 2.4 GHz. Ova arhitektura pojačala snage koristi ulazni i izlazni hibridni sprežnik za postizanje širokog propusnog pojasa, gdje je moguće dobiti izvrsno ulazno i izlazno prilagođenje, neovisno o prilagodnim mrežema pojedinih pojačala arhitekture. Ulazni i izlazni sprežnici projektirani su u double-box tehnici kako bi se postigao velik frekvencijski pojas, a karateristike sprežnika optimirane su koristeći elektromagnetske simulacije fizičkog dizajna. Sprežnik je implementiran i karateriziran na posebnoj pločici i postiže širinu pojasa od 800 MHz, i razliku u fazi dvaju izlaznih signala od 89.6° na 2.4 GHz. Mikrotrakaste prijenosne linije korištene su za projektiranje prilagodnih mreža i mreža za napajanje, a optimalne impedancije za pojedine tranzistore pronađene su korištenjem sustava za karakterizaciju tranzistora u režimu velikog signala. Za napajanje, korištena je četvrtvalna prijenosna linija, koja, uz visoku impedanciju prema napajanju na fundamentalnoj frekvenciji, daje i nisku impedanciju na frekvenciji drugog harmonika, što povećava korisnost pojačala snage u klasi AB. Izrađeno HCBT balanced pojačalo snage na 2.4 GHz, postiže izlaznu snagu od 21.4 + /-0.18 dBm, pojačanje snage od 10.4 + /-0.15 dB, korisnost kolektora najmanje 36%

u propusnom pojasu, i širinu frekvencijskog pojasa od 700 MHz. Performanse pojačala snage usporedive su ili bolje od pojačala snage implementiranih u nekima od skupljih poluvodičkih tehnologija.

Zadnje poglavlje "*Conclusion*", daje osvrt na glavne rezultate dobivene u sklopu provedenog istraživanja, i preporuke za daljnji rad u području karakterizacije HCBT-a u režimu velikog signala i projektiranja RF pojačala snage, kako u diskretnoj, tako i u integriranoj tehnici.

**Ključne riječi**: bipolarni tranzistor s horizontalnim tokom struje (HCBT), bipolarni tranzistori, režim velikog signala, skalarni sustav za karaterizaciju u režimu velikog signala, vektorski sustav za karaterizaciju u režimu velikog signala, mjerenje visokofrekvencijskih valnih oblika, područje linearnog rada, pojačala snage, Doherty.

## **Contents**

| 1. | Intro | oduction | n                                       | 1  |

|----|-------|----------|-----------------------------------------|----|

|    | 1.1.  | Wirele   | ss communications                       | 1  |

|    |       | 1.1.1.   | Radiofrequency spectrum                 | 1  |

|    |       | 1.1.2.   | Wireless communication standards        | 2  |

|    |       | 1.1.3.   | Modern modulated signals                | 4  |

|    | 1.2.  | Radiof   | requency transmitter                    | 5  |

|    | 1.3.  | Radiof   | requency power amplifier                | 7  |

|    |       | 1.3.1.   | Small-signal operation                  | 7  |

|    |       | 1.3.2.   | Large-signal operation                  | 9  |

|    |       | 1.3.3.   | Performance parameters                  | 11 |

|    |       | 1.3.4.   | Classes of operation                    | 13 |

|    |       | 1.3.5.   | Load-pull                               | 18 |

|    |       | 1.3.6.   | Measured performance                    | 20 |

|    | 1.4.  | Efficie  | ncy enhancement                         | 21 |

|    |       | 1.4.1.   | Doherty PA                              | 21 |

|    |       | 1.4.2.   | Envelope Tracking PA                    | 22 |

|    | 1.5.  | Bandw    | ridth enhancement                       | 23 |

|    | 1.6.  | Transis  | stor technologies for power amplifiers  | 24 |

|    |       | 1.6.1.   | Evolution of transistor technology      | 24 |

|    | 1.7.  | Bipola   | r transistor for power amplifiers       | 26 |

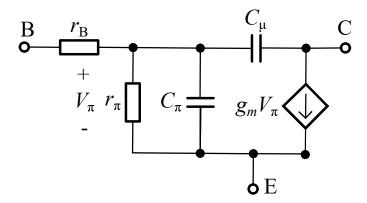

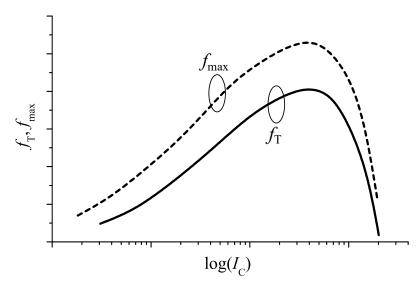

|    |       | 1.7.1.   | Small-signal equivalent schematic       | 26 |

|    |       | 1.7.2.   | Large-signal equivalent schematic       | 28 |

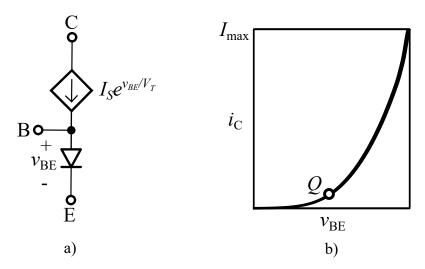

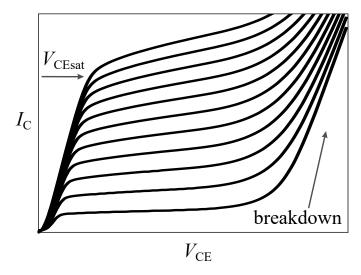

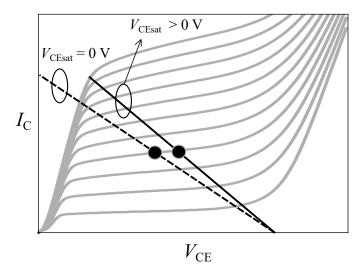

|    |       | 1.7.3.   | Output DC characteristics               | 30 |

|    |       | 1.7.4.   | Maximum voltage and current swing       | 33 |

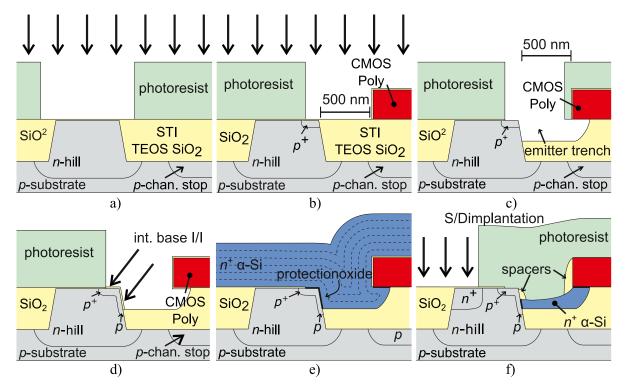

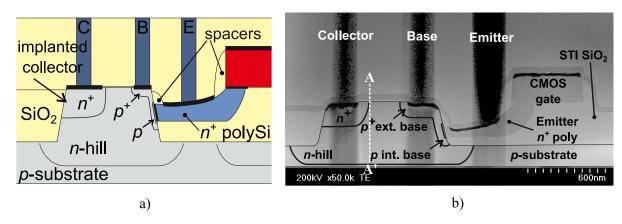

|    | 1.8.  | Horizo   | ental Current Bipolar Transistor (HCBT) | 34 |

|    |       | 1.8.1.   | HCBT fabrication                        | 34 |

|    |       | 1.8.2.   | HCBT electrical characteristics         | 37 |

|    |       | 183      | Collector region design                 | 41 |

| 2. | Larg                    | ge-signa                     | d characteristics of horizontal current bipolar transistor |  |  |  |  |

|----|-------------------------|------------------------------|------------------------------------------------------------|--|--|--|--|

|    | 2.1.                    | Measu                        | rement methodology                                         |  |  |  |  |

|    | 2.2.                    | Load-p                       | oull/source-pull setup                                     |  |  |  |  |

|    |                         | 2.2.1.                       | DUT and test fixture                                       |  |  |  |  |

|    | 2.3.                    | Class-A                      | A/AB/B performance                                         |  |  |  |  |

|    |                         | 2.3.1.                       | Output DC characteristics and load line analysis           |  |  |  |  |

|    |                         | 2.3.2.                       | Large-signal performance parameters                        |  |  |  |  |

|    |                         | 2.3.3.                       | Load-pull and source-pull analysis                         |  |  |  |  |

|    | 2.4.                    | Impact                       | of collector doping on large-signal performance 61         |  |  |  |  |

|    |                         | 2.4.1.                       | Transistor electrical parameters                           |  |  |  |  |

|    |                         | 2.4.2.                       | DC characteristics                                         |  |  |  |  |

|    |                         | 2.4.3.                       | Load-pull analysis                                         |  |  |  |  |

| 3. | Line                    | ar oper                      | rating area of horizontal current bipolar transistor       |  |  |  |  |

|    | 3.1.                    | Linear                       | operating area of a bipolar transistor                     |  |  |  |  |

|    |                         | 3.1.1.                       | Measurement setup                                          |  |  |  |  |

|    |                         | 3.1.2.                       | Measurement methodology                                    |  |  |  |  |

|    |                         | 3.1.3.                       | Linear operating area and maximum output power             |  |  |  |  |

|    | 3.2.                    | Impact                       | of load line hard-limitation on bias point                 |  |  |  |  |

|    |                         | 3.2.1.                       | Base bias configurations                                   |  |  |  |  |

|    |                         | 3.2.2.                       | Analysis by simulation                                     |  |  |  |  |

| 4. | Doh                     | erty pov                     | wer amplifier                                              |  |  |  |  |

|    | 4.1.                    | Active                       | load modulation                                            |  |  |  |  |

|    |                         | 4.1.1.                       | Full output power                                          |  |  |  |  |

|    |                         | 4.1.2.                       | 6-dB output power back-off                                 |  |  |  |  |

|    | 4.2. Load-pull analysis |                              |                                                            |  |  |  |  |

|    | 4.3.                    | ing network design           |                                                            |  |  |  |  |

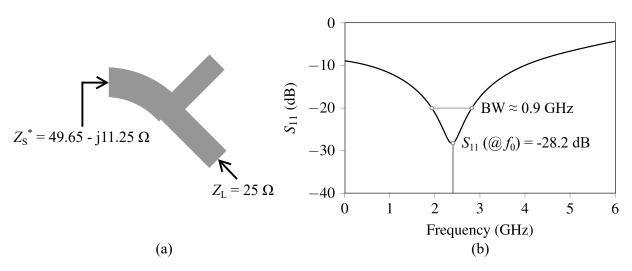

|    |                         | 4.3.1.                       | Main PA output matching network                            |  |  |  |  |

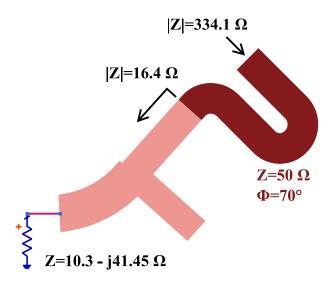

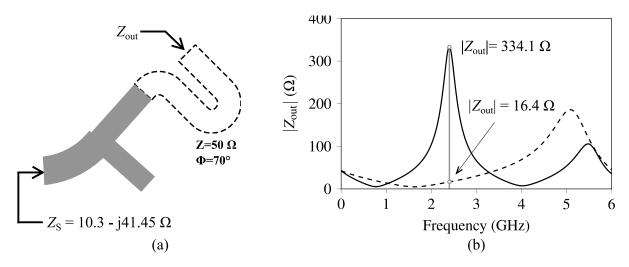

|    |                         | 4.3.2.                       | Peaking PA output matching network                         |  |  |  |  |

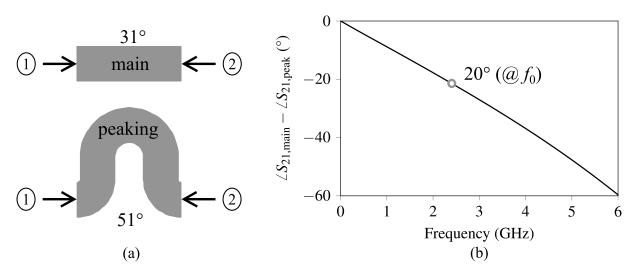

|    |                         | 4.3.3.                       | Input signal split and phase shift                         |  |  |  |  |

|    |                         | 4.3.4.                       | Output quarter-wave transformer                            |  |  |  |  |

|    | 4.4. Implementation     |                              |                                                            |  |  |  |  |

|    | 4.5.                    | 5. Measurement results       |                                                            |  |  |  |  |

| 5. | Bala                    | nced po                      | ower amplifier                                             |  |  |  |  |

|    | 5.1.                    | 1. Bandwidth and return loss |                                                            |  |  |  |  |

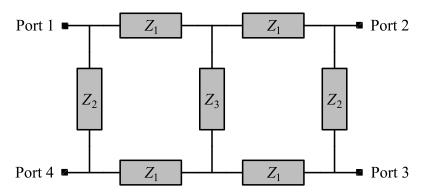

|    | 5.2.                    | Branchline coupler           |                                                            |  |  |  |  |

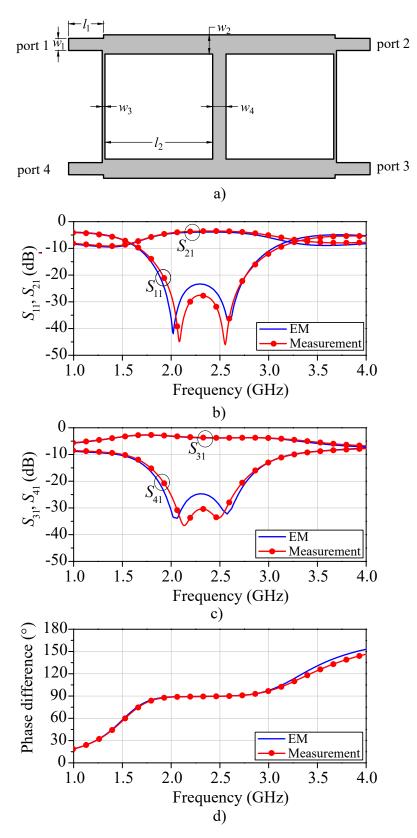

|     |        | 5.2.1.     | Double-box branchline coupler        | 124 |

|-----|--------|------------|--------------------------------------|-----|

|     |        | 5.2.2.     | Microstrip branchline coupler design | 125 |

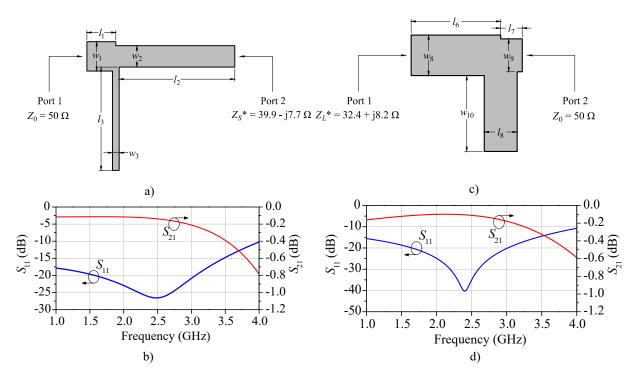

|     | 5.3.   | Optima     | matching impedances                  | 127 |

|     | 5.4.   | Input a    | nd output matching networks          | 128 |

|     | 5.5.   | Bias no    | work                                 | 129 |

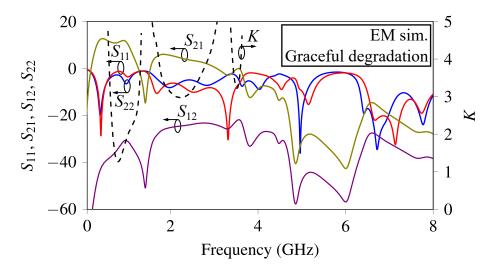

|     | 5.6.   | Small-     | ignal simulations                    | 130 |

|     | 5.7.   | Schem      | tic and fabricated amplifier         | 131 |

|     | 5.8.   | Measu      | ement results                        | 133 |

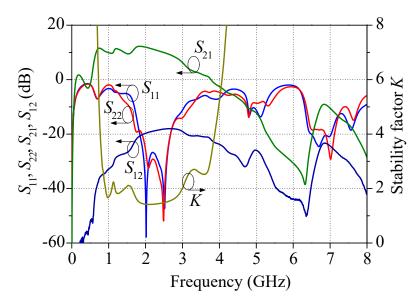

|     |        | 5.8.1.     | Small-signal performance             | 133 |

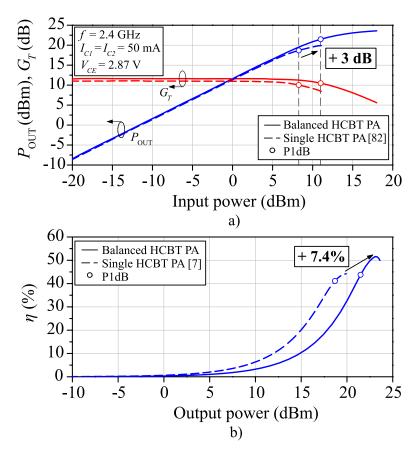

|     |        | 5.8.2.     | Large-signal performance             | 134 |

|     | 5.9.   | Compa      | rison with state-of-the-art          | 137 |

| 6.  | Con    | clusion    |                                      | 138 |

| Bil | bliogr | aphy .     |                                      | 141 |

| Bi  | ograp  | <b>ohy</b> |                                      | 153 |

| Ži  | votop  | is         |                                      | 156 |

## **Chapter 1**

### Introduction

The connectivity of people and devices tremendously evolved over the last decade with the proliferation of high-speed and low-latency communications. Countless smartphones, computers, and gadgets, employ such a connectivity to collect data and perform tasks to increase the quality of our lives. The key enabler of this ubiquitous connectivity are wireless communications, the fastest growing segment of the communications industry.

#### 1.1 Wireless communications

The vision of wireless connectivity where every device, vehicle, sensor, or home appliance, is connected to a common network and communicates efficiently real-time and all the time, is a tendency of both the industry and academic research [1]. Nowadays, the wireless communications market grows at a remarkable pace due to high-performance handheld devices, usually termed smartphones, with the ability to create multimedia materials of high quality and send them across the world at an instant. Additionally, the automotive industry is adopting the wireless communications in the form of radars of a small form factor, which can detect and thereby prevent the collision if the driver fails to react. More importantly, the wireless connectivity plays a crucial role for the networks which predict or analyze the events hazardous to human life, such as massive networks of wireless-enabled sensors monitoring fire hazards, hazardous waste sites, stress and strain in buildings and bridges, or the spread of chemicals and gasses at a disaster site. Therefore, the wireless communications provide a means of monitoring the places and processes which are difficult or impossible to approach by a human, or observe over a wired network.

#### 1.1.1 Radiofrequency spectrum

Wireless communications employ radiofrequency waves to send and receive the information over the air. The frequencies of interest for the modern wireless communications are placed in the range from 300 MHz to 300 GHz. The frequency range is further segmented in multiple frequency bands for easier reference, as shown in Tab. 1.1 [2, 3], where the letter designations for radar systems are also shown due to their widespread use in commercial wireless communications. Although the bands span up to the visible light, the majority of commercial wireless communications nowadays operate in the range from 300 MHz to 6 GHz, wherein the most of the commercial wireless communication standards are defined.

**Table 1.1:** Designations of frequency bands according to International Telecommunication Union [2] (left), and radar frequency bands according to The Institute of Electrical and Electronics Engineers (IEEE) [3] (right).

| Band no. | Symbols | Frequency range |

|----------|---------|-----------------|

| 3        | ULF     | 300 - 3000 Hz   |

| 4        | VLF     | 3 - 30 kHz      |

| 5        | LF      | 30 - 300 kHz    |

| 6        | MF      | 300 - 3000 kHz  |

| 7        | HF      | 3 - 30 MHz      |

| 8        | VHF     | 30 - 300 MHz    |

| 9        | UHF     | 300 - 3000 MHz  |

| 10       | SHF     | 3 - 30 GHz      |

| 11       | EHF     | 30 - 300 GHz    |

| 12       |         | 300 - 3000 GHz  |

| 13       |         | 3 - 30 THz      |

| 14       |         | 30 - 300 THz    |

| 15       |         | 300 - 3000 THz  |

| Band designation | Frequency range |

|------------------|-----------------|

| HF               | 3 - 30 MHz      |

| VHF              | 30 - 300 MHz    |

| UHF              | 300 - 1000 MHz  |

| L                | 1 - 2 GHz       |

| S                | 2 - 4 GHz       |

| С                | 4 - 8 GHz       |

| X                | 8 - 12 GHz      |

| Ku               | 12 - 18 GHz     |

| K                | 18 - 27 GHz     |

| Ka               | 27 - 40 GHz     |

| V                | 40 - 75 GHz     |

| W                | 75 - 110 GHz    |

| mm               | 110 - 300 GHz   |

#### 1.1.2 Wireless communication standards

The development of wireless communication standards is mainly driven by the preferences of the users, thus, roughly every ten years a new standard generation brings new applications along with a significant increase in performance [4].

#### First generation (1G)

The basic service in the first generation of mobile communications was voice calling. The coverage was excellent, but due to the different proprietary standards in different countries, completely different equipment was needed when travelling from one country to another.

#### Second generation (2G)

The second generation of mobile communications was a synonym for the most widespread Global System for Mobile Communication (GSM) standard. The GSM brought along the widely used short messaging service (SMS). Additionally and more significantly, the GSM offered first data transfer service with the speed of 9.6 kbps. Later on, the General Packet Radio Services (GPRS) and Enhanced Data Rates Service (EDGE) increased the speed to several tens of kilobits and 1-200 kpbs, respectively.

#### Third generation (3G)

The third generation, on the other hand, is a synonym for Universal Mobile Telecommunication System (UMTS). The most significant novelty is a data transfer speed of 2 Mbps. Nevertheless, the end-user speed did not go above 364 kbps, which made UMTS not as quite successful. Only did the later introduction of High-Speed Uplink Packet Access (HSUPA) and High-Speed Downlink Packet Access (HSDPA) bring more popularity, supporting several tens of megabits per second. This, for the first time, enabled the access to the e-mail service over a wireless network.

#### Fourth generation (4G)

The main wireless communication standard in the fourth generation is Long-Term Evolution (LTE) [5]. The standard is still evolving nowadays, with the highest speeds of 1 Gbps, whereas the voice calling service is transferred to the Internet Protocol (IP), called voice-over-IP, which enables much higher voice quality with respect to legacy solutions.

#### Fifth generation (5G) and beyond

The deployment of the fifth generation of mobile communications is currently in progress, whereas the specifications for the sixth generation are also debated among the industry and regulatory bodies. The newest generations, besides the sub-6 GHz spectrum, employ the milimeter-wave spectrum which enables much wider channel bandwidths and, therefore, higher data throughputs [6].

#### Wi-Fi

The above mentioned standards are based on a concept of frequency reuse wherein the network is spatially divided in cells [1]. Although not a cellular network, one of the most important wireless communication standards in use is wireless fidelity or Wi-Fi. It enables high-speed wireless connections of smaller area coverage than the cellular networks, commonly used for indoor

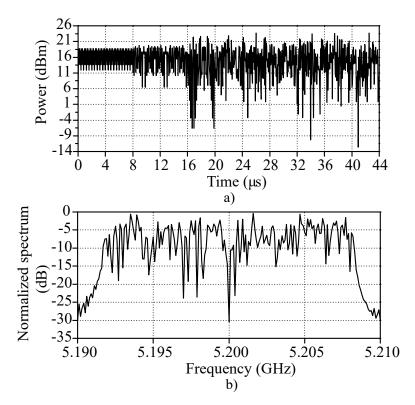

**Figure 1.1:** Power (a) and spectrum (b) of 802.11a standard-compliant OFDM signal at the carrier frequency of 5.2 GHz and bandwidth of 20 MHz.

high-performance wireless communication. The Wi-Fi has a lot in common with the modern cellular networks since the LTE is developed by borrowing the traits of the physical network layer from the Wi-Fi. More precisely, both 4G LTE, 5G, and Wi-Fi, employ the same signal modulation, which is used in digital wireless communications to imprint the digital information to the radiofrequency signal, namely, Orthogonal Frequency Division Multiplex (OFDM).

#### 1.1.3 Modern modulated signals

The characteristics of the radiofrequency signal transmitted over the air are modulated in accordance to the digital information being sent. The goal of the modulation is to send as much as possible bits of information in a given time period and over a given bandwidth, usually termed spectral efficiency and measured in b/s/Hz. The OFDM is a modulation of choice for all modern wireless communication standards since it provides the highest spectral efficiency and, additionally, a way to combat the multipath propagation [1]. The example OFDM-modulated signal is shown in Fig. 1.1 both in time and frequency domains. The main characteristics of such a modulated signal is a power which varies in time and a relatively wide bandwidth. In the time domain, the signal is formatted in time frames, which can be discerned from Fig. 1.1a. For example, at the beginning of the transmission (t = 0 s), there is a guard interval of 8  $\mu$ s in which no information bits are being sent. Besides the bandwidth, some information is also visible from the spectrum in Fig. 1.1b, e.g., there is no carrier frequency of 5.2 GHz in the

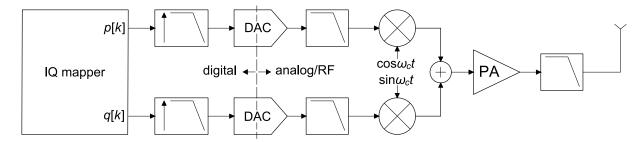

**Figure 1.2:** Block diagram of a direct up-conversion (DU) or zero-intermediate frequency (ZIF) transmitter. The transmitter is divided in digital and analog/RF part. The IQ mapping and oversampling take place in digital domain. Digital signal is converted to analog signal and passed to the reconstruction filter for the rejection of unwanted spectrum images of the baseband signal. The signal is then amplified, filtered, and passed to the antenna for the transmission.

transmitted signal, since carrier alone does not carry the information. To further investigate the characteristics of the modulated signals employed in wireless communications, an overview of the architecture and operation of a radiofrequency transmitter is given in the following.

#### 1.2 Radiofrequency transmitter

The transmitter is responsible for modulating the digital information onto the carrier frequency. There are many ways to perform this task and, consequently, there are many transmitter architectures. The choice of wireless transmitter architecture depends on many factors, which are mainly dictated by the application and communication standard that the transmitter operates in. Some of the most important parameters to consider are performance, bandwidth, complexity of implementation, output power, and cost.

Due to its simplicity and low cost, a direct up-conversion (DU,) also called zero-intermediate frequency (ZIF), transmitter architecture recently became popular in cellular radio systems [7, 8, 9, 10]. This architecture does not employ an intermediate-frequency mixing stage and provides more flexibility in designing multi-standard, multi-band transmitters for modern radio systems [11]. An example of this radiofrequency transmitter architecture is shown in Fig. 1.2. The resulting modulated bandpass signal at the output of the transmitter is given by [12]

$$s(t) = \Re\{\tilde{s}(t)e^{j\omega_0 t}\},\tag{1.1}$$

where  $\omega_c$  is the carrier frequency, whereas  $\tilde{s}(t)$  is a complex modulated baseband signal given by

$$\tilde{s}(t) = p(t) + jq(t), \tag{1.2}$$

where p and q are in-phase and quadrature components of the baseband signal, respectively.

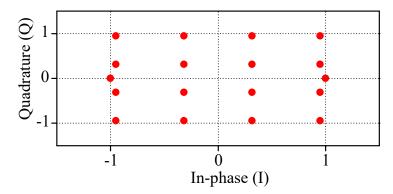

**Figure 1.3:** Constellation of the 802.11a-compliant OFDM signal. The constellation consists of both the BPSK and 16QAM points.

The transmitter can be separated in two main parts; the digital and analog section. The two differ with respect to the signals being processed. Additionally, the analog part deals with both the low-frequency baseband signals and radiofrequency signals to be transmitted.

Both p and q signals are processed separately in the transmitter. The s(t) is a sum of sine waves with amplitude and phase determined according to the wireless communication standard employed. Firstly, the digital representation of a complex modulated bandpass signal  $\tilde{s}(t)$  is generated in the IQ mapper according to the constellation of the modulation. The constellation diagram of the signal from Fig. 1.1 is shown in Fig. 1.3. Each constellation point carrier certain number of information bits. The shown constellation is, actually, composed of two separate modulations; Binary Phase Shift Keying (BPSK) with two points at (-1, 0) and (1, 0), and Quadrature Amplitude Modulation with the rest 16 points (16QAM). The two modulations are part of the OFDM modulation scheme used in Wi-Fi.

Information bits are assigned (mapped) to the constellation points of the modulation and the p and q are then created entirely in the digital domain [13]. Hence, sampled versions of p(t) and q(t), p[t] and p[t], are output from the IQ mapper. Such sampled signals exhibit spectrum that repeats itself at the multiples of the sampling frequency  $f_s$ . The frequency separation between those unwanted spectrum images usually implies filters with high roll-off that are difficult to design. Because of that, the signals are delivered to the oversampling stage to increase this frequency separation and relax the constraints on the reconstruction filter that comes later in the transmitter chain. Oversampling is implemented in the digital domain by zero padding the original digital signal [13]. The oversampled signals are then converted to analog domain using the digital to analog converters (DACs) and unwanted spectrum images are filtered out by the reconstruction filter stage. The baseband analog signals, p(t) and q(t), are then upconverted to the carrier frequency  $f_c$  such that the quadrature component is multiplied with the sine function and the in-phase component with the cosine function. The signals are then summed, resulting in a signal given by (1.1), and delivered to the power amplifier. Finally, the signal is amplified by the power amplifier stage and filtered to reject out-of-band emission

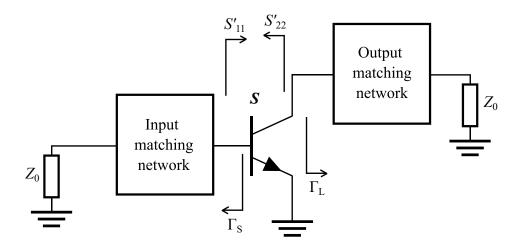

**Figure 1.4:** Block schematic of the amplifier for small-signal analysis with a bipolar transistor as an active device.

resulting from the nonlinearity of the power amplifier, and lastly, the signal is fed to the antenna.

#### 1.3 Radiofrequency power amplifier

The bandpass signal of (1.1) is usually of insignificant power when output from the summation stage. Since the range of wireless communication is determined to a large extent by the power of the radiated signal, an amplification is needed to increase the power of this signal. A radiofrequency power amplifier (PA) amplifies the bandpass signal to be transmitted over the wireless communication channel. It dissipates the greatest amount of power in the transmitter. Furthermore, while amplifying the useful bandpass signal, it generates an in-band distortion that degrades the quality of the transmitted signal, and out-of-band distortion that pollutes adjacent frequency channels in use by other users. Additionally, power amplifiers for modern radio systems need to be efficient and also highly linear to provide signals of sufficient quality for a proper demodulation at the receiver side.

#### 1.3.1 Small-signal operation

A power amplifier excited by a signal of a small enough amplitude so that neither voltage nor current swing is limited at the terminals of the amplifier, is operating in the small-signal regime. It is assumed in this regime that the output signal is a linear function of the input signal. The performance of such an amplifier can be analysed and predicted employing a linear analysis. To analyze the amplifier in the small-signal regime, scattering parameters, termed *S* parameters, are readily employed [14]. Due to the difficulty of measuring voltage and current at high frequencies, an *S* parameter is defined as a ratio of two voltage travelling waves at specified measurement planes, called reference planes.

The block schematic of an amplifier used for small-signal analysis is shown in Fig. 1.4 [15]. The active device providing the necessary gain is a transistor of a bipolar or metal-oxide-semiconductor (MOS) type. Regardless of the technology, a transistor is described by

$$\mathbf{S} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \tag{1.3}$$

where S is the S-matrix of the transistor. The input and output matching networks are passive networks used to match the impedance of the transistor to the system impedance  $Z_0 = 50~\Omega$ . The matching networks resonate out the parasitics of the transistor so that the maximum gain is achieved for a given active device. The transformation is contained in the reflection coefficients  $\Gamma_S$  and  $\Gamma_L$  for the input and output, respectively. Since the matching networks are passive, the following applies:

$$|\Gamma_{\mathbf{S}}| < 1, \tag{1.4}$$

and

$$|\Gamma_{\rm L}| < 1. \tag{1.5}$$

It can be shown that the input and output impedances are a function of the output and input networks, respectively [14]. The reflection coefficient looking into the input port of the transistor,  $S'_{11}$ , is given by

$$S'_{11} = S_{11} + \frac{S_{12}S_{21}\Gamma_{L}}{1 - S_{22}\Gamma_{L}},\tag{1.6}$$

whereas the reflection coefficient looking into the output port of the transistor,  $S'_{22}$ , by

$$S_{22}' = S_{22} + \frac{S_{12}S_{21}\Gamma_{S}}{1 - S_{11}\Gamma_{S}}. (1.7)$$

To achieve maximum transfer of the signal from the source to the input port of the transistor, the input matching network is designed so that

$$S_{11}' = \overline{\Gamma_{S}}. (1.8)$$

Similarly, the output matching network is designed so that the maximum signal transfer is achieved from the output port of the transistor to the load:

$$S_{22}' = \overline{\Gamma_{L}}. (1.9)$$

One important parameter regarding the stability of the amplifier, termed Rollet's stability factor k, can be calculated as

$$k = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |D|^2}{2S_{12}S_{21}}. (1.10)$$

wherein D is a determinant of the S. The k parameter gives the information about the stability of the amplifier; if k > 1, it can be shown that both  $|\Gamma_S| < 1$  and  $|\Gamma_L| < 1$ , which are constraints which need to be met if the passive matching networks are to be designed. In other words, k > 1 ensures a stable small-signal operation of the amplifier. If (1.8) and (1.9) are fulfilled, the gain of the amplifier is equal to the  $S_{21}$  parameter of the transistor.

Although the small-signal analysis assumes a linear relationship between the output and input signals, the nonlinearities arise in the small-signal range due to the nonlinearities of the transistor. These nonlinearities are usually described by a power series

$$v_o = a_1 v_i + a_2 v_i^2 + a_3 v_i^3 + a_4 v_i^4 + \dots +, \tag{1.11}$$

where  $v_i$ ,  $v_o$ , and  $a_i$ , are input voltage, output voltage, and voltage gain of the transistor, respectively, and are sometimes called weakly nonlinear effects [15], since they arise in the small-signal (linear) regime. The weakly nonlinear effects are the cause of intermodulation distortion which results in the in-band distortion.

#### 1.3.2 Large-signal operation

In a normal operation, however, a power amplifier is operating with signals which are comparable in amplitude to its maximum current and voltage ratings. Therefore, such signals, for certain input power levels, experience clipping at the terminals of the amplifier. Since the clipping of the voltage and/or current waveforms is a distortion of the signal, such a regime is termed large-signal operation. Therefore, these nonlinearities are termed strongly nonlinear effects since they occur in large-signal operation.

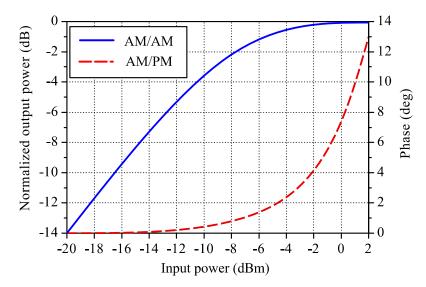

The large-signal performance of an example power amplifier is shown in Fig. 1.5. The performance entails output power (AM/AM) and phase (AM/AM) of the output signal as a function of the power of the input signal at the fundamental (carrier) frequency [16]. Due to the strongly nonlinear effects present, the output power does not increase linearly with the input power, in high-power range. The increase of output power becomes smaller and, at certain input power levels, saturates. The region of the transfer characteristics in which the output power increase starts to deviate from the linear function, is called a compression. Additionally, the phase difference between the output and input signals is also a function of the input power. The gain of the amplifier is, therefore, decreasing due to the output power saturation.

**Figure 1.5:** Transfer characteristics of a power amplifier at the fundamental frequency. The dependence of output power (AM/AM) and phase (AM/PM) on input power are shown.

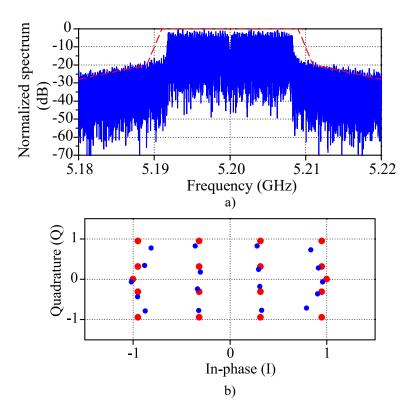

The impact of large-signal operation on the output signal is shown in Fig. 1.6, where the spectrum and constellation diagram of the OFDM signal from Fig. 1.1 is shown at the output of the power amplifier operating in the compression region. The input power is high enough so that, besides weakly nonlinear effects, the strongly nonlinear effects also have significant impact on the output signal. As shown in Fig. 1.6a, the power is radiated in the neighbouring frequency bands, thus interfering with other communication channels. Additionally, an example of a spectrum mask is shown, which defines the maximum power in the adjacent frequency bands with respect to the channel power. The mask is defined for all wireless communication standards in order to limit the interference between the adjacent channels [17]. In the example shown in the figure, the power amplifier outputs higher power in the adjacent bands than the allowed by the communication standard. Furthermore, due to the clipping of the voltage and current waveforms at the output of the amplifier, the output signal contains significant power at the harmonics of the the carrier frequency, usually termed the fundamental frequency.

The spectrum of the signal gives information about the output power in the adjacent bands, but not about the quality of the transmitted information. To analyze the quality of the transmitted signal, the signal should be demodulated by the receiver so that the received signal can be compared to the transmitted one. The constellation of the transmitted signal of Fig. 1.6a, is shown in Fig. 1.6b. The constellation points deviate from the reference constellation of Fig. 1.3. The probability of a receiver demodulating the information of a specific constellation point depends on how far the point is from its reference location. Therefore, due to the difference between the transmitted signal's constellation and the ideal one, the probability of a demodulation error is higher, thus, increasing the bit error rate (BER) of the communication channel.

Linearity constraints are becoming increasingly difficult to satisfy because of the complex modulations envisioned for the future wireless communications employing dense constellation

**Figure 1.6:** Spectrum (a) and constellation diagram (b) of a 802.11a-compliant OFDM signal from Fig. 1.1 for the power amplifier operating in compression. The spectrum mask [17] (red dashed line) shown in (a) for reference. Both the transmitted (blue dots) and reference (red dots) constellation diagrams shown in (b) for reference.

diagrams [4], e.g. 1024QAM or 4096QAM. Although the large-signal operation of the power amplifier negatively impacts the performance of the wireless communication channel, the necessary output power to achieve a desired communication range is usually set near the compression region. If the input signal power is decreased to achieve a linear response, the performance of the power amplifier degrades significantly. In other words, the power amplifier operates with the optimal performance in the compression, which can be described employing the performance parameters of the power amplifier.

#### **1.3.3** Performance parameters

The performance of the power amplifier is described by a different set of parameters with respect to small-signal amplifiers. The most important performance parameters of a power amplifier directly influencing the performance of the transmitter are:

• Output power - a power delivered from the output of the amplifier to the load at the fundamental frequency, defined by

$$P_{\text{OUT}} = \frac{1}{2} \Re\{V_{\text{OUT}} \overline{I_{\text{OUT}}}\}, \tag{1.12}$$

where  $P_{\text{OUT}}$ ,  $V_{\text{OUT}}$ , and  $\overline{I_{\text{OUT}}}$ , are real output power, output voltage phasor, and a complex-conjugate of the output current phasor, respectively.

• Gain - a ratio of the output power and the input power, defined by

$$G = \frac{P_{\text{OUT}}}{P_{\text{IN}}},\tag{1.13}$$

where G and  $P_{IN}$  are the gain and input power of the amplifier.

Collector/drain efficiency - a ratio of the output power and DC power consumed, defined by

$$\eta = \frac{P_{\text{OUT}}}{P_{\text{DC}}} \cdot 100\%,\tag{1.14}$$

where  $P_{DC}$  is a DC power consumed by the amplifier. Since  $\eta$  does not take into account the input RF power, power-added efficiency (PAE) is defined by

PAE =

$$\frac{P_{\text{OUT}} - P_{\text{IN}}}{P_{\text{DC}}} = \eta \left( 1 - \frac{1}{G} \right) \cdot 100\%,$$

(1.15)

where PAE is the power-added efficiency of the amplifier.

• Linearity - defined separately for in-band and out-of-band signals. The out-of-band emissions are taken into account by adjacent channel power ratio (ACPR), defined by

$$ACPR = \frac{P_{ADJ}}{P_{MAIN}},$$

(1.16)

where  $P_{\rm ADJ}$  and  $P_{\rm MAIN}$  are powers of the adjacent and main channel, respectively. This measure is limited by the communication standards and, in general, should be as low as possible. The example of a power amplifier exhibiting high ACPR is shown in Fig. 1.6a. The in-band linearity is described by measuring the difference between the transmitted and ideal constellation diagrams and averaging over time frames, the process which is also defined in the respective standards. The parameter quantifying the in-band linearity of the power amplifier is error vector magnitude (EVM), defined by [18]

$$EVM_{rms} = \frac{\sqrt{\frac{1}{N} \sum_{i=1}^{N} |S_{ideal,i} - S_{meas,i}|^2}}{\sqrt{\frac{1}{M} \sum_{i=1}^{M} |S_{ideal,i}|^2}},$$

(1.17)

where  $S_{\text{ideal,i}}$  and  $S_{\text{meas,i}}$  are the ideal and measured (transmitted) constellation points, respectively. The calculation of EVM is done over many symbols (N) and then normal-

ized, which is defined by a factor M. In essence, the EVM is a ratio of the root mean square value of all the error vectors, averaged over N symbols, and then divided by some normalization factor.

The performance of a power amplifier is directly influenced by the chosen circuit architecture. Thus, the performance parameters are dependent on the chosen transistor, bias point, input and output matching impedances seen by the transistor, and the class of operation.

#### 1.3.4 Classes of operation

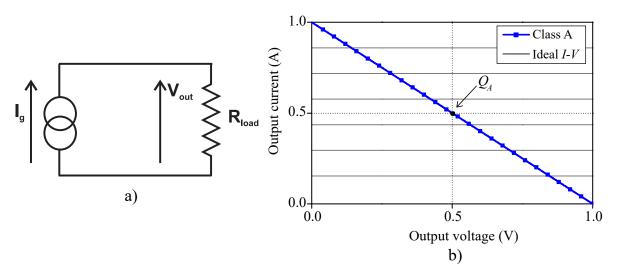

A power amplifier can operate in different classes of operation, depending on the bias level, load impedance, and input signal. Since the output is of a main concern, the ideal equivalent schematic of the output of the power amplifier is shown in Fig. 1.7a. The schematic consists of a current generator and a load resistor. The current generator represents an ideal behaviour of the output of a transistor, be it a bipolar or a MOS [15]. The current generator provides the current  $I_g$  to the load resistor  $R_{load}$ . The result of this is the output voltage  $V_{out}$ , which is set across the load resistor. The output power can now be calculated as

$$P_{\text{OUT}} = \frac{1}{2} V_{\text{out}} I_{\text{g}} = \frac{1}{2} I_{\text{g}}^2 R_{\text{load}}.$$

(1.18)

where  $I_g$  and  $V_{out}$  are the amplitudes of the current through, and voltage across the resistor  $R_{load}$ . According to (1.18), the output power can be increased indefinitely by increasing the load resistance  $R_{load}$  or current  $I_g$ , wherein the latter is increased by increasing the amplitude of the input signal. This fact is the result of the current generator not having maximum current and voltage ratings. On the other hand, a transistor operates reliably up to a certain voltage and current values, which then directly define the maximum allowed voltage and current amplitudes at the terminals of the transistor. Since the load resistance and input power, therefore, determine the voltage and current amplitudes, respectively, their value should be selected such that the maximum voltage and current values at the output are not higher than the maximum allowed values for a given active device.

Therefore, the load resistance and input power define the load line at the output of the transistor. If it is assumed that the maximum voltage and current values supported by the transistor are, for simplicity, defined by

$$V_{\text{max}} = 1 \text{ V}, \tag{1.19}$$

and

$$I_{\text{max}} = 1 \text{ A}, \tag{1.20}$$

**Figure 1.7:** (a) Ideal equivalent schematic of the output of the power amplifier and (b) load line for Class-A operation. The output *I-V* characteristics of the current generator from (a) are also shown.

then, the maximum output power for a given transistor is achieved when the load line is defined as in Fig. 1.7b.

#### Class-A

Both the voltage and current swing from 0 V to 1 V and 0 A to 1 A, respectively. The bias point and load impedance are set such that the maximum voltage and current swings are achieved. Thus, the bias point is

$$Q_{\rm A} = (I_{\rm QA}, V_{\rm QA}) = (0.5 \text{ A}, 0.5 \text{ V}),$$

(1.21)

where  $I_{QA}$  and  $V_{QA}$  are DC current and voltage in bias point  $Q_A$ , respectively. The load resistance is given by

$$R_{\text{load}} = \frac{V_{\text{out}}}{I_{\text{g}}} = \frac{0.5}{0.5} = 1 \ \Omega.$$

(1.22)

It is evident from (1.21) and (1.22) that the amplitudes of the voltage and current,  $V_{\text{out}}$  and  $I_{\text{g}}$ , are equal to 0.5 V and 0.5 A, respectively. Then, according to (1.18), the maximum output power for this transistor,  $P_{\text{OUT,max}}$ , is

$$P_{\text{OUT,max}} = \frac{1}{2} \cdot 0.5 \cdot 0.5 = 125 \text{ mW}.$$

(1.23)

where  $I_g = (1/2)I_{\text{max}}$  and  $V_{\text{out}} = (1/2)V_{\text{max}}$ . Furthermore, the collector efficiency (a bipolar transistor assumed) is

**Figure 1.8:** (a) Load line and (b) voltage and current waveforms of the fundamental frequency  $f_0 = 2$  GHz for a Class-B power amplifier.

$$\eta = \frac{0.125}{0.5 \cdot 0.5} \cdot 100\% = 50\%. \tag{1.24}$$

The parameters calculated in (1.21) - (1.24) are for the Class-A power amplifier. Therefore, a Class-A PA provides the maximum output power for a given transistor while exhibiting a collector efficiency of 50 %.

It is assumed in this analysis that the input power is set at the level for which the current  $I_g$  swings from 0 A to 1 A. For lower input power, the output power is also lower, whereas the DC power is the same, thus, the efficiency is lower. For example, according to (1.24), for a 3-dB lower output power in Class-A operation, the collector efficiency drops to 25%. For a higher input power, the amplifier enters the compression region at the output [see Fig. 1.5], wherein the clipping of the voltage  $V_{\text{out}}$  and current  $I_g$  occurs due to the nonlinearities of the transistor. Additionally, the higher input power results in the higher output power which causes the voltage and current swings to go above the maximum values  $V_{\text{max}}$  and  $I_{\text{max}}$ . Therefore, the  $P_{\text{OUT,max}}$  is a maximum output power if the current and voltage swings are to be kept at their maximum values.

Additionally, the gain of the Class-A power amplifier is equal to the small-signal gain, which, if (1.8) and (1.9) are satisfied, is equal to  $S_{21}$  parameter of the transistor. Therefore, the Class-A PA provides the small-signal gain and linear response for lower input powers, which is a great advantage for achieving high linearity.

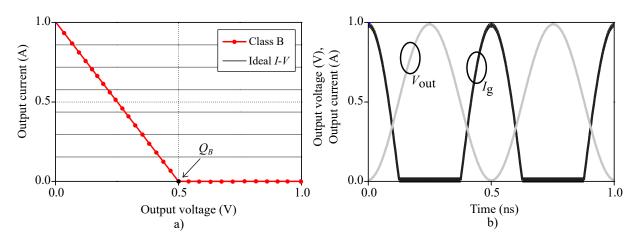

#### **Class-B**

Although the Class-A provides a linear response, the efficiency is only 50%. According to (1.14), the collector efficiency can be increased by increasing the output power or by decreasing the DC power. The maximum output power is limited by the transistor, and, therefore, cannot be

increased above a certain value. On the other hand, the DC power can be decreased to achieve higher collector efficiency.

Since the power amplifier is operating with large signals, the DC current  $I_Q$  can be set, e.g., to 0 A, when there is no input signal present. Thus, the output current waveform resembles that of the half-wave rectified sine wave. The load line for such a mode of operation, termed Class-B, is shown in Fig. 1.8. Since the DC current is set to 0 A, the transistor (current source) conducts current only for the positive half-wave of the current waveform, whereas for the negative one, the transistor's cut-off region does not allow the negative current swing at the output. Due to the clipping of the current waveform, the output current signal contains the harmonics of the fundamental frequency. The voltage is, on the other hand, a full sine wave as is the case for the Class-A operation; there are no harmonics in the spectrum of the output voltage  $V_{\text{out}}$ . This is achieved by placing a parallel resonant tank of high quality factor across the load resistor  $R_{\text{load}}$ . The tank has its resonant frequency set at the fundamental frequency so that the harmonics get shorted to ground, whereas the fundamental frequency gets dissipated in the load. The voltage and current waveforms for Class-B operation are shown in Fig. 1.8b.

If the input power is set such that the current and voltage swing to  $I_{\text{max}}$  and  $V_{\text{max}}$ , the DC current is the DC component of the half-wave sine wave, given by

$$I_{\rm QB} = \frac{I_{\rm max}}{\pi} = 0.32 \,\mathrm{A}.$$

(1.25)

$$Q_{\rm B} = (I_{\rm OB}, V_{\rm OB}) = (0.32 \text{ A}, 0.5 \text{ V}),$$

(1.26)

where the  $I_{QB}$  is lower with respect to  $I_{QA}$ . The output power of Class-B PA can be found once the amplitude of the fundamental component of the current is determined. For a half-wave rectified sine wave, which swings from 0 to  $I_{max} = 1$  A, the fundamental component is given by

$$I_{\rm g} = \frac{I_{\rm max}}{2} = 0.5 \,\mathrm{A},$$

(1.27)

which is exactly equal to the amplitude of the current in Class-A operation. Thus, the output power is also the same and given by (1.23), whereas the collector efficiency is

$$\eta = \frac{0.125}{0.32 \cdot 0.5} \cdot 100\% = 78.5\%. \tag{1.28}$$

Therefore, a Class-B PA provides the same output power as Class-A, but with higher collector efficiency of 78.5%.

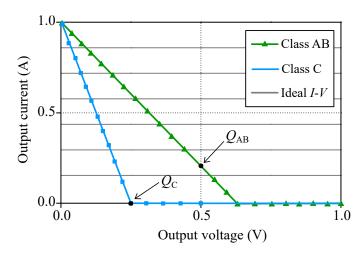

Figure 1.9: Load lines for Class-AB and Class-C power amplifiers.

#### **Class-AB**

The bias point can be set in-between the Class-A and Class-B operation, resulting in Class-AB operation shown in Fig. 1.9. The input power is again chosen so that the current swings up to  $I_{\text{max}}$ . The transistor conducts for more than only half of the period as in Class-B, therefore, the DC current is

$$I_{\mathrm{QB}} < I_{\mathrm{QAB}} < I_{\mathrm{QA}}, \tag{1.29}$$

whereas the collector efficiency is

$$50\% < \eta < 78.5\%. \tag{1.30}$$

#### Class-C

Even higher efficiencies than Class-B can be achieved by further lowering the bias point so that the transistor conducts for shorter than half of the period of the fundamental signal. This operation is termed Class-C. The load line for this class is shown in Fig. 1.9. The Class-C is highly nonlinear and, therefore, not considered as a linear class of operation, but efficiencies higher than 78.5% can be achieved.

The load resistance  $R_{\rm load}$  for each class of operation is chosen such that the maximum output power is achieved, i.e., so that the voltage and current swing up to the maximum allowed values of the active device. This resistance, which results in maximum output power, is termed the optimal load resistance. Interestingly, this load resistance is exactly equal for Class-A and Class-B, whereas for Class-AB, it deviates insignificantly from the Class-A and Class-AB values [15]. Furthermore, all classes except Class-A, require parallel resonant tank at the output to short the voltage harmonics to ground. Only then the maximum efficiencies can be achieved

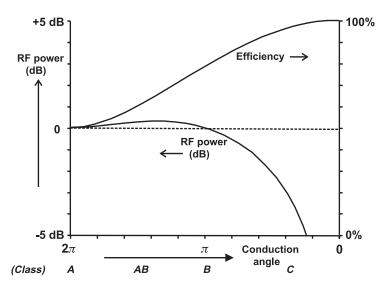

**Figure 1.10:** Output power and collector efficiency of the Class-A, Class-AB, Class-B, and Class-C, with respect to the Class-A. The load resistance is set at the optimal value and the ideal harmonic short is assumed [15].

in the respective classes. The performance of the four classes regarding the output power and collector efficiency is summarized in Fig. 1.10 [15]. The output power is the same for classes A and B, whereas drops significantly for Class-C. The output power is slightly higher in Class-AB. The classes are sometimes differentiated by the conduction angle; a value which states what fraction of the signal's period transistor conducts current. Thus, for Class-A and Class-B it is equal to  $2\pi$  and  $\pi$ , respectively.

Therefore, the efficiency of a power amplifier can be increased simply by decreasing the DC current, i.e., by reducing the conduction angle of the transistor. But, once the DC current is lower, the harmonics occur due to the clipping of the current waveform, and the performance degrades since the power is transferred to the harmonics, which is an unwanted effect. To mitigate this, a parallel resonant tank is employed to short the harmonic components of the voltage to ground and, thus, restore the voltage to a pure sine wave. Thus, more efficient classes require additional circuitry at their output, which might become difficult to implement at high frequencies. Nevertheless, the linear classes are still widely used both as a standalone amplifiers, and as a part of advanced PA architectures.

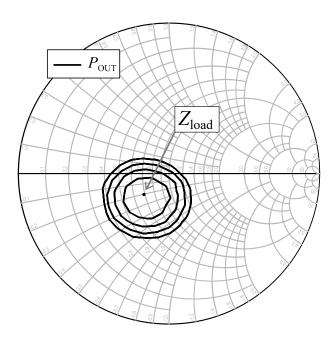

#### 1.3.5 Load-pull

The optimal load resistance is a load resistance for which the maximum output power is achieved. In the simplified schematic shown in Fig. 1.7a, the output of the transistor is represented as a current source and, thus, to achieve maximum output power, the  $R_{load}$  should be connected at the output. Regardless of the type of the transistor used, there are significant parasitic reactances associated with the transistor. In that case, the output of the transistor should be matched by the optimal load impedance,  $Z_{load}$ , wherein the reactive part of  $Z_{load}$  cancels out the reactances

Figure 1.11: Example of a load-pull measurement.

of the transistor. The real part of  $Z_{load}$  is the optimal load resistance  $R_{load}$ . The difficulty of determining the optimal load impedance lies in the fact that the maximum allowed voltage and current values limit the maximum output power available at the output of the transistor. Additionally, the parasitics of a transistor are highly nonlinear and difficult to analytically take into account. Thus, the optimal load impedance for maximum output power is usually determined by measurements in which the load impedance is varied until the maximum output power is measured. Such measurements are termed load-pull measurements.

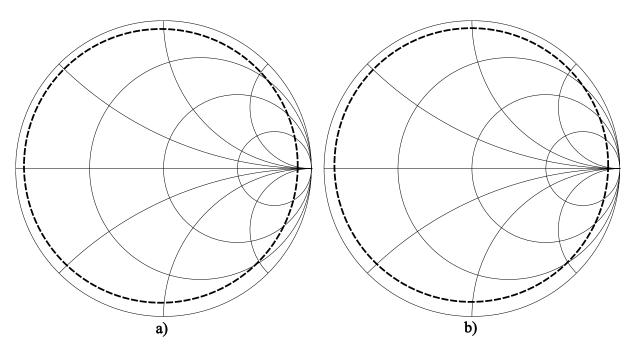

Although the small-signal analysis states that for the maximum signal transfer the load should be a complex-conjugate of the impedance of a transistor, the complex-conjugate match does not ensure the maximum output power [15]. For power amplifiers, the load-pull measurements are employed to empirically find the load impedance for which the maximum output power or, in some cases, maximum collector efficiency is achieved. The example results of a load-pull measurement are shown in the Smith chart in Fig. 1.11. The load impedance is varied and the output power is measured. The data is then interpolated so that the lines of equal output power are drawn. Since there is only one  $Z_{load}$  for which the maximum output power is achieved, the function has one maximum, which occurs in the center of the lines of equal output power. These lines are termed load-pull contours [15], and they approximate an elliptical shape. The contours provide an information about the change of output power when the load impedance deviates from the optimal value  $Z_{load}$ . For the example from Fig. 1.11, the optimal load impedance is  $Z_{load} = 35 - j10 \Omega$ . Therefore, the capacitance of  $10 \Omega$  is to cancel the parasitic inductance of the transistor's output.

**Figure 1.12:** Measured performance of a Class-A power amplifier at the fundamental frequency  $f_0 = 2.4 \, \text{GHz}$ .

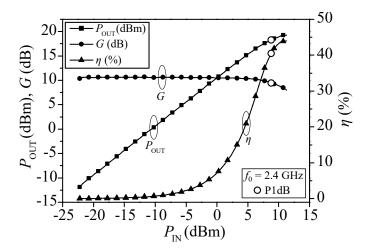

#### 1.3.6 Measured performance

The analysis presented so far assumes one level of input power for which the maximum current and voltage swings are achieved. For this input power, both output power and collector efficiency are at their maximum values. The measured performance of a fabricated power amplifier differs somewhat with respect to the simplified analysis of Fig. 1.7a, mainly because the transistor cannot be represented by an ideal current source.

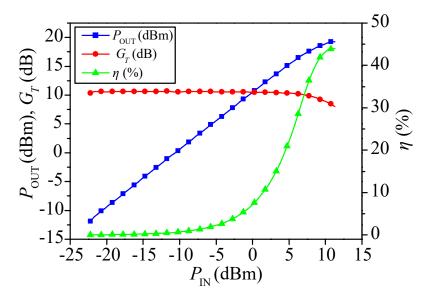

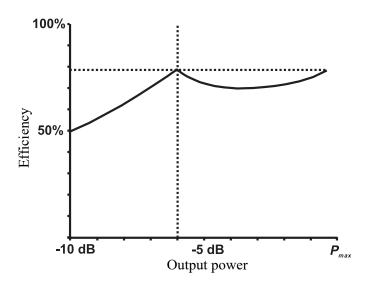

The example of a measured performance of a Class-A power amplifier is shown in Fig. 1.12. The figure shows output power  $P_{OUT}$ , gain G, and collector efficiency  $\eta$ , as a function of input power  $P_{IN}$ , for a Class-A power amplifier operating at the fundamental frequency  $f_0$  of 2.4 GHz. The output power characteristic comprises two main parts; the linear input power range, in which the linear relationship between the input and output is maintained, and the large-signal region, where the gain compression occurs and the output power does not increase linearly with input power. The gain is constant in the small-signal range, whereas it decreases in the compression region. The input power for which the gain drops by 1 dB (P1dB), is usually taken as the boundary between the linear and compression regions. For the linear classes of operation, a P1dB is the point of maximum output power, above which high nonlinearity occurs and, thus, the PA is not operated.

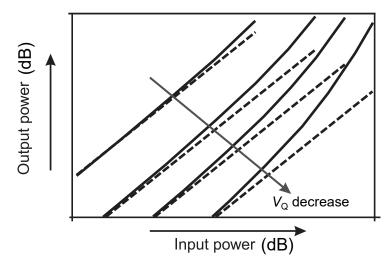

The collector efficiency shows an exponential increase for low input powers and a maximum in the compression region. Interestingly, the collector efficiency maximum occurs for output power higher than P1dB. The maximum, thus, is seldom reached in normal operation, but still, the efficiency is the highest for the maximum output power of P1dB. Therefore, in the power range of interest, the power amplifier operates with the highest efficiency in P1dB, whereas for lower input power, it drops significantly. As shown in Fig. 1.12, the efficiency in P1dB is 40%, whereas for 3-dB lower input power it is 22%; the collector efficiency of a power amplifier

depends on the power of the input signal. This fact makes power amplifier extremely difficult to design for high efficiency while operating with modern modulated signals.

As shown in Fig. 1.1a, the power of a modulated signal varies in time. The signal shown in the figure has more than 10-dB difference between the peak and average power. This value is termed peak to average power ratio (PAPR) and is important figure of merit for the modern modulated signals. The PAPR is defined as

$$PAPR = \frac{P_{\text{peak}}}{P_{\text{avg}}},\tag{1.31}$$

where  $P_{\text{peak}}$  and  $P_{\text{avg}}$  are peak and average power of the modulated signal, respectively. The power amplifier from Fig. 1.12 has a collector efficiency of 6% for a 10-dB lower input power with respect to P1dB. Thus, the collector efficiency also varies with time for a modulated excitation. The average collector efficiency is then a proper measure of efficiency for a given input signal, which can be quite low for high-PAPR input signals of 802.11a standard [19]. It should be noted, however, that the efficiency depends on the technology of implementation and architecture of the power amplifier, as shown in the following.

# 1.4 Efficiency enhancement

The efficiency of the power amplifier directly impacts the end-user experience during wireless communication; by employing more efficient power amplifier, the battery in a handheld device lasts longer. On the other hand, the efficiency of a power amplifier operating in a base station determines the cooling costs needed for a reliable operation. For a power amplifier of high efficiency, the DC dissipation is lower for the same output power, thus, the generated heat is also lower. Since the efficiency is by far the most important parameter of the power amplifiers employed in modern wireless communications, there are specific circuit architectures which maximize the efficiency while, usually, sacrificing the linearity and complexity. There are two main techniques to increase the efficiency of a power amplifier; load modulation and power supply modulation.

# 1.4.1 Doherty PA

The Doherty power amplifier modulates the load impedance in order to keep the transistor optimally matched both for full output power and for lower output powers [20]. The power range lower than the full output power of a power amplifier is usually termed output power back-off (OPBO).

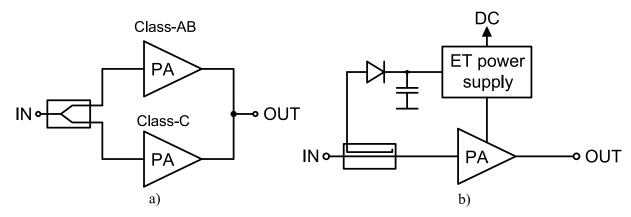

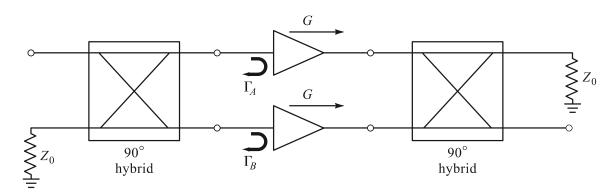

The simplified block schematic of a Doherty amplifier is shown in Fig. 1.13a. The Doherty comprises two separate power amplifiers, usually Class-AB and Class-C, connected in parallel

**Figure 1.13:** Simplified block schematic of (a) Doherty and (b) Envelope Tracking high-efficiency power amplifiers.

at the output. The input signal is split at the input by employing a signal splitter, usually in the form of a hybrid coupler [14], whereas the output signal is combined again at the output. In its most basic form, the Doherty splits the input signal equally, and then the input signals are fed to the power amplifiers. The Class-AB amplifier is configured such that it is active for all values of output power, whereas the Class-C is driven to conduction for higher input powers, which is, for a 3-dB split at the input, at the 6-dB output power back-off. By injecting the signal into the load, the Class-C PA effectively modulates the load impedance presented to the Class-AB PA. This load modulation is configured such that the maximum efficiency is achieved in the entire 6-dB output power back-off range. Therefore, for signals exhibiting PAPR of 6 dB, the ideal symmetrical Doherty provides the maximum efficiency equal to the value achieved for the maximum output power.

# 1.4.2 Envelope Tracking PA

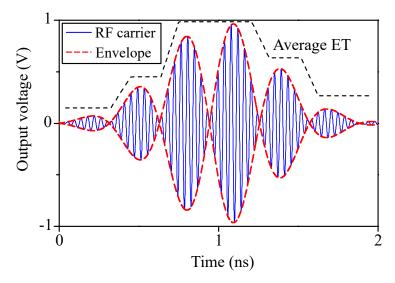

The efficiency can also be increased by modulating the supply voltage of the power amplifier. Since the supply voltage is set at the value to ensure the maximum voltage swing for the maximum output (input) power, once the input signal power is decreased, the supply voltage can also be decreased to accommodate the reduced swing at the output [21]. In this way, the efficiency is increased by reducing the DC power dissipated by the PA. Such an operation is a characteristic of the Envelope Tracking (ET) architecture, the simplified block diagram of which is shown in Fig. 1.13b. The input signal power is varying in accordance with the envelope of the signal. Thus, to enable the change of the power supply voltage with the input power, the envelope is extracted from the input signal by a directional coupler [14], and fed to the envelope detector. The envelope is the input to the ET power supply, which modulates the supply voltage of the PA in rhythm with the envelope, i.e., the input power. This concept is shown in Fig. 1.14, wherein the carrier signal and its envelope are shown. Due to the large dips in signal power, the requirements on the ET power supply are extremely harsh and their efficiency can be as low as

Figure 1.14: The concept of Envelope Tracking power supply.

60%, which then lowers the overall efficiency of the ET power amplifier. The technique termed average Envelope Tracking mitigates this problem by tracking the envelope in discrete steps. But, the possible efficiency increase is lower since the DC power is still wasted in the envelope dips. In the modern transmitters, the envelope is generated in the digital domain, converted to the analog by DACs, and then brought to the input of a fast DC-DC converter which supplies the PA.

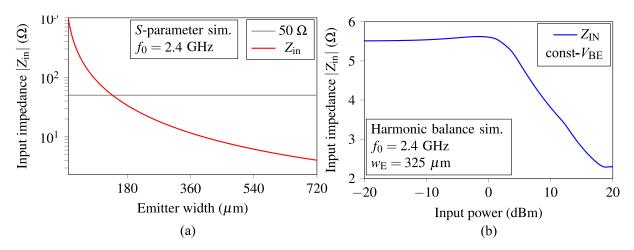

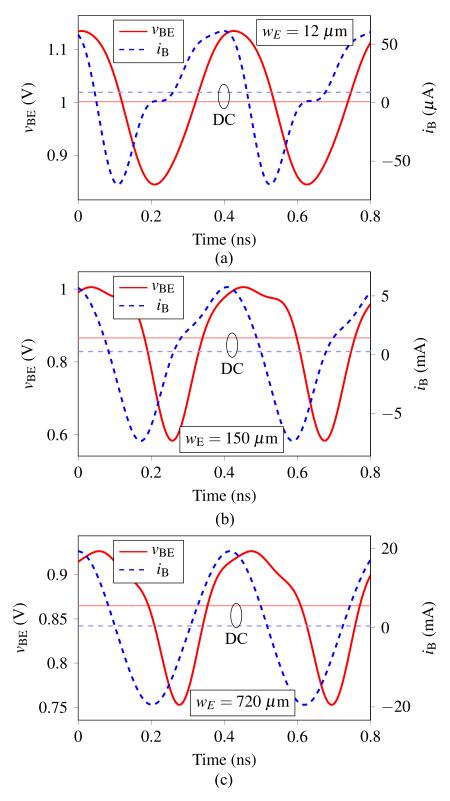

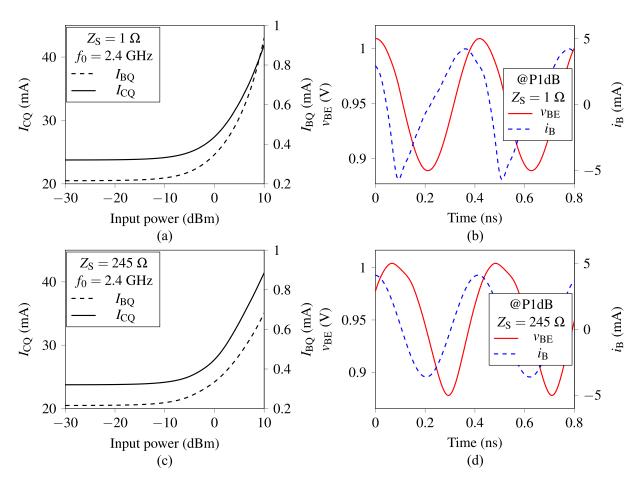

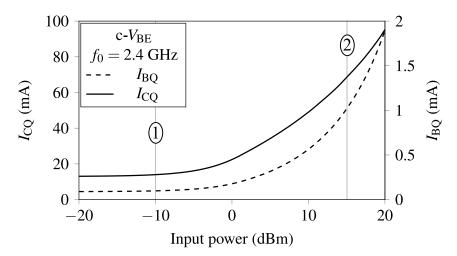

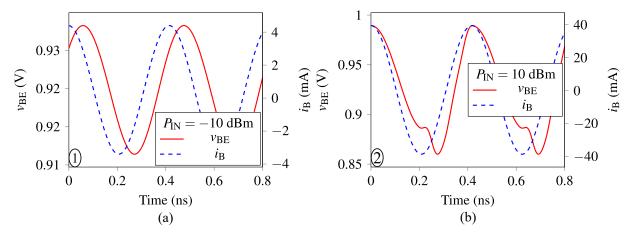

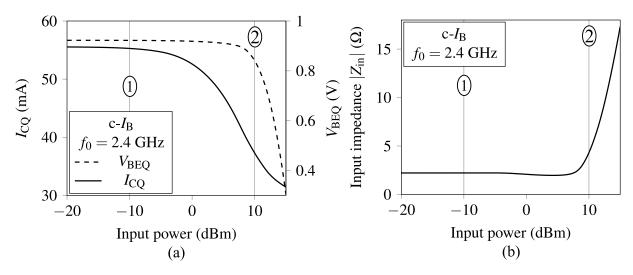

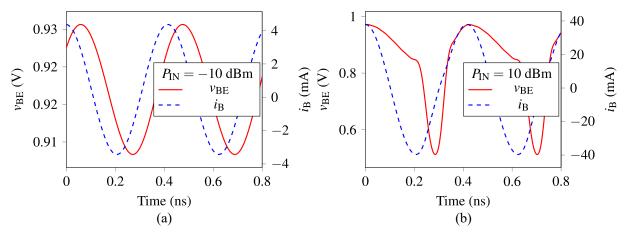

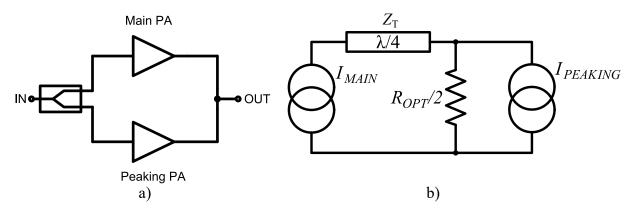

#### 1.5 Bandwidth enhancement