# Improving performance in software internet routers through compact lookup structures and efficient datapaths

Zec, Marko

**Doctoral thesis / Disertacija**

2019

Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Faculty of Electrical Engineering and Computing / Sveučilište u Zagrebu, Fakultet elektrotehnike i računarstva

Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:168:455203

Rights / Prava: In copyright/Zaštićeno autorskim pravom.

Download date / Datum preuzimanja: 2024-04-19

Repository / Repozitorij:

FER Repository - University of Zagreb Faculty of Electrical Engineering and Computing repozitory

#### FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

#### Marko Zec

## IMPROVING PERFORMANCE IN SOFTWARE INTERNET ROUTERS THROUGH COMPACT LOOKUP STRUCTURES AND EFFICIENT DATAPATHS

**DOCTORAL THESIS**

Supervisors: Associate Professor Miljenko Mikuc, PhD Professor Luigi Rizzo, PhD

## FAKULTET ELEKTROTEHNIKE I RAČUNARSTVA

#### Marko Zec

# POBOLJŠANJE IZVEDBE PROGRAMSKIH INTERNETSKIH USMJERITELJA POMOĆU KOMPAKTNIH PREGLEDNIH STRUKTURA I EFIKASNIH PODATKOVNIH STAZA

**DOKTORSKI RAD**

Mentori:

izv. prof. dr. sc. Miljenko Mikuc prof. dr. sc. Luigi Rizzo

| Zavodu za telekomunikacije.       |  |  |  |  |  |  |

|-----------------------------------|--|--|--|--|--|--|

|                                   |  |  |  |  |  |  |

| Mentori:                          |  |  |  |  |  |  |

| izv. prof. dr. sc. Miljenko Mikuc |  |  |  |  |  |  |

| prof. dr. sc. Luigi Rizzo         |  |  |  |  |  |  |

|                                   |  |  |  |  |  |  |

| Doktorski rad ima: 77 stranica    |  |  |  |  |  |  |

| Doktorski rad br.:                |  |  |  |  |  |  |

Doktorski rad izrađen je na Sveučilištu u Zagrebu, Fakultetu elektrotehnike i računarstva, na

#### **Mentor's Curriculum Vitae**

Miljenko Mikuc is an Associate Professor at the University of Zagreb, Faculty of Electrical Engineering and Computing, Department of Telecommunications. He graduated in 1987. and received his PhD in the field of technical sciences, electrical engineering in 1997. from the University of Zagreb, Faculty of Electrical Engineering and Computing (FER).

He has participated on seven scientific projects of the Ministry of Science, Education and Sports of the Republic of Croatia and on the international project "Verification and validation methods for formal descriptions (COST 247). He participated and led projects with "The Boeing Company - IDS, LabNet Analysis, Modeling Simulation and Experimentation", "International Computer Science Institute / University of California, Berkeley", "The FreeBSD Foundation", multi-year research project in the field of information and communication technology with Ericsson Nikola Tesla d.d., "Customized IMUNES for Ericsson (E-IMUNES)" and IRI-project "New Generation Lawful Interception System - NG LI", where FER is a partner of the company SedamIT d.o.o.

At the University of Zagreb, Faculty of Electrical Engineering and Computing, he is responsible for the following undergraduate and graduate courses: "Digital Logic", "Network Programming", "Internet Security" and "Network and Services Management." At the postgraduate doctoral study program, he is responsible for "Formalisms in Telecommunications" and "Communication Protocols - Selected Topics". As a mentor, he successfully led more than 200 undergraduate and graduate students, while at the postgraduate study he was a mentor for 15 master theses and 3 doctoral theses.

He has published over 40 scientific and professional papers in journals and conference proceedings in the field of communication networks, protocols, virtualization, formal methods and security. He is a member of a professional association of IEEE. He participates in the work of the Technical Program Committee of the International Scientific Conference of SoftCOM and as a reviewer at a number of international conferences.

## Životopis mentora

Miljenko Mikuc je izvanredni profesor na Zavodu za telekomunikacije Fakulteta elektro-tehnike i računarstva Sveučilišta u Zagrebu. Diplomirao je 1987. godine a doktorsku disertaciju iz područja tehničkih znanosti, polja elektrotehnika, "Postupci provjere ispravnosti specifikacije telekomunikacijskih procesa" obranio je 1997. godine.

Sudjelovao je kao istraživač na sedam znanstvenih projekata Ministarstva znanosti, obrazovanja i sporta Republike Hrvatske te na međunarodnom projektu "Verification and validation methods for formal descriptions (COST 247)". Bio je voditelj dva projekta Primjene informa-

cijske tehnologije pod pokroviteljstvom Ministarstva znanosti i tehnologije Republike Hrvatske. Bio je voditelj projekata suradnje s "The Boeing Company - IDS, LabNet Analysis, Modeling Simulation and Experimentation", "International Computer Science Institute", "The FreeBSD Foundation" iz SAD-a te višegodišnjeg istraživačkog projekta u sklopu suradnje na području informacijskih i komunikacijskih tehnologija s kompanijom Ericsson Nikola Tesla d.d., "Prilagođen IMUNES za Ericsson (E-IMUNES)". Voditelj je IRI-projekta "Nova generacija rješenja za zakonsko presretanje podataka - NG LI" na kojem je FER partner tvrtke prijavitelja SedamIT d.o.o.

Sudjeluje u nastavi na preddiplomskom i diplomskom studiju kao nositelj ili su-nositelj predmeta "Digitalna logika", "Mrežno programiranje", "Sigurnost u Internetu" i "Upravljanje mrežom i uslugama". Na poslijediplomskom studiju su-nositelj je predmeta "Formalizmi u telekomunikacijama" i "Odabrana poglavlja komunikacijskih protokola". Pod njegovim mentorstvom uspješno je završilo studij više od 200 studenata na preddiplomskom i diplomskom studiju. Na poslijediplomskom studiju bio je mentor pri izradi 15 magistarskih radova te 3 doktorska rada.

Objavio je preko 40 znanstvenih i stručnih radova u časopisima i zbornicima konferencija u području komunikacijskih mreža, protokola, virtualizacije, formalnih metoda i sigurnosti. Član je stručne udruge IEEE. Sudjeluje u radu tehničkog programskog odbora međunarodne znanstvene konferencije SoftCOM, te kao recenzent na većem broju međunarodnih konferencija.

### Mentor's Curriculum Vitae

Luigi Rizzo is a Professor of Computer Engineering at the Universita' di Pisa, Italy. His research focuses on computer networks and operating systems. He has published over 50 academic papers, including highly cited works on network emulation, scalable reliable multicast and multicast congestion control, packet scheduling, high speed network I/O and virtual machine networking. His research projects received funding from the European Commission, as well as many industrial partners including Microsoft, Cisco, Intel, Netapp, Verisign.

Much of his work has been implemented and deployed in popular operating systems and applications, and widely used by the research community. His contributions include the popular dummynet network emulator (a standard component of FreeBSD and OS/X, and now also available for Linux and Windows); one of the first publicly available erasure code for reliable multicast; the qfq packet scheduler; and the netmap framework for fast packet I/O.

Prof. Rizzo has been a visiting researcher at several industrial and academic research institutions, including ICSI (UC Berkeley), Intel Research Cambridge (UK), Intel Research Berkeley, and recently Google Mountain View. He has served as General Chair for SIGCOMM 2006, TPC Co-Chair for SIGCOMM 2009 and CoNEXT 2014, and TPC member/reviewer for a number networking conferences and journals.

## Životopis mentora

Luigi Rizzo je profesor računalnog inženjerstva na Sveučilištu Pisa, Italija. Glavna područja njegovih istraživanja su računalne mreže i operacijski sustavi. Objavio je preko 50 radova koji su citirani više od 8000 puta, uključujući radove o emulaciji računalnih mreža, skalabilnog pouzdanog višeodredišnog odašiljanja i kontrole zagušenja višeodredišnog odašiljanja, raspoređivanja paketa, brzog dohvaćanja i odašiljanja paketa, te umrežavanja virtualnih strojeva. Njegovi istraživački projekti bili su financirani sredstvima Europske komisije, kao i brojnih industrijskih partnera, uključujući Microsoft, Cisco, Intel, Netapp, Verisign.

Velik dio njegovih radova implementiran je i ugrađen u popularne operacijske sustave i aplikacije, te široko prihvaćen u istraživačkoj zajednici. Njegovi doprinosi uključuju popularni alat za emulaciju mreža dummynet koji je standardna komponenta operacijskih sustava FreeBSD i OS/X, te je dostupan i za Linux i Windows OS; jedan od prvih javno dostupnih brišučih kodova za pouzdano višeodredišno odašiljanje; algoritam raspoređivanja paketa QFQ; te prilagodni sloj za brzo dohvaćanje i odašiljanje paketa netmap.

Prof. Rizzo bio je gostujući istraživač na nizu industrijskih i sveučilišnih istraživačkih institucija, uključujući (UC Berkeley), Intel Research Cambridge (UK), Intel Research Berkeley, te trenutno Google Mountain View. Predsjedao je znanstvenim skupom SIGCOMM 2006, su-

predsjedao tehničkim programskim odborom skupova SIGCOMM 2009, CoNEXT 2014, te je bio član programskih odbora ili recenzent niza časopisa i skupova iz područ računalnih mreža.

## Acknowledgments

Prof. Miljenko Mikuc and prof. Luigi Rizzo were great and patient advisors, and I thank them and congratulate them both on finally graduating me. Jointly writing and polishing the original DXR paper, which set the foundation for this thesis, was among the most fun and rewarding experiences I recall in my whole career.

Most likely I would have never got this thesis complete without additional guidance from a shadow advisor, prof. Maja Matijašević. Her help was also instrumental in getting the more recent results documented and published in a decent form.

Denis Salopek set up our physical evaluation testbed and did the most of the benchmarking and profiling work on a prototype packet processor based on DXR, the results of which unfortunately could not be included in this thesis, but led to ironing out several subtle bugs in the DXR library and the Click element.

Most of all, I wish to thank my wife Nataša and our kids for being patient and supportive with me wasting time on stop-and-go efforts around this thesis over just too many years. Well, it's finally done!

### **Abstract**

Expensive, inflexible, closed yet fast hardware packet datapath implementations have dominated the high-speed and core Internet routing scene over the past two decades due to both real and perceived lack of performance offered by software routers running on commodity hardware. Today, software routers are mostly displaced to edge functions where the throughput pressure is lower, or to applications where flexibility takes precedence over performance.

This thesis challenges the aforementioned status-quo by asserting that the performance potential of contemporary multi-core microprocessors for applications in Internet routing datapaths may be significantly greater than what is currently thought. The results suggest that significant improvements in software-based Internet routing performance may be achieved by carefully engineering data structures and algorithms to permit modern microprocessors to efficiently leverage their fast and sizable cache hierarchies, thereby extracting more parallelism across multiple execution cores, while preserving the precious main memory bandwidth for packet input and output, or other memory-intensive input / output tasks.

The research presented here focuses on longest prefix matching (LPM) as a fundamental operation which simultaneously presents a major performance bottleneck and implementation challenge in Internet Protocol (IP) routers, hardware and software based alike. The proposed algorithm and the accompanying data structures sustain nearly 3.5 billion random LPM lookups per second in a contemporary routing database containing 739,561 IPv4 prefixes with 148 unique next-hops, while running on conventional, commodity PC hardware. The same configuration can exceed 7 billion lookups per second with locality in the stream of lookup keys. The thesis dissects how the principles and techniques applied in the design and implementation of the experimental prototype contribute to achieving those throughput levels.

Keywords: IP lookups, LPM, software packet processors, software routers, router performance

# Poboljšanje izvedbe programskih internetskih usmjeritelja pomoću kompaktnih preglednih struktura i efikasnih podatkovnih staza - prošireni sažetak

Tijekom proteklih dvadesetak godina programski ostvarene usmjeritelje temeljene na mikroprocesorskim platformama opće namjene u jezgri Interneta su u potpunosti istisnuli iz upotrebe visokopropusni ali skupi, zatvoreni, i nefleksibilni usmjeritelji temeljeni na specijaliziranim sklopovljima. Ovaj rad preispituje navedeni status-quo hipotezom da potencijal modernih višejezgrenih mikroprocesora može biti dostatan za učinkovitu primjenu u podatkovnim stazama brzih Internetskih usmjeritelja. Rezultati pokazuju da se povećanje propusnosti programski ostvarenih usmjeritelja može postići pažljivim odabirom i konstrukcijom podatkovnih struktura i algoritama koji modernim mikroprocesorima omogućuju dobro iskorištenje predmemorija, što se posredno odražava i učinkovitim paralelnim izvođenjem na više procesorskih jezgri uz malu učestalost pristupa glavnoj memoriji, čija sabirnica više vremena ostaje slobodna za prihvat i odašiljanje paketa, te za ostale memorijski zahtjevne ulazno / izlazne zadaće. Disertacija je usredotočena na problem pretraživanja tablica usmjeravanja najduljim prefiksnim podudaranjem (engl. longest prefix matching, LPM) kao temeljni postupak odlučivanja pri obradi paketa u Internetskim usmjeriteljima. Predložene nove klase algoritama s pripadajućim podatkovnim strukturama tijekom izvođenja na računalu opće namjene omogućuju postizanje propusnosti od približno 3.5 milijarde pretraživanja u sekundi temeljem nezavisnih, slučajno odabranih ključeva u tablici s 739.561 IPv4 zapisa i 148 moguća odredišta, preuzetoj iz usmjeritelja u jezgri Interneta. Uz pretraživanje s uzastopnim ponavljanjem slučajno odabranih ključeva postiže se propusnost do 7 milijardi upita u sekundi. U radu se analizira kako načela i postupci primjenjeni u oblikovanju i ostvarenju eksperimentalnog prototipa doprinose postizanju ovakvih razina propusnosti.

Rad je podijeljen u sedam poglavlja.

U prvom, uvodnom poglavlju, identificiran je istraživački problem, motivacija i ciljevi istraživanja te je dan opis strukture rada. Izložen je kratak pregled razvoja tehnologije usmjeritelja namjenjenih radu u jezgri Interneta. Opisana je tranzicija od široke primjene programski ostvarenih usmjeritelja tijekom devedesetih godina prošlog stoljeća, do njihovog kasnijeg potpunog napuštanja i zamjene specijaliziranim sklopovskim izvedbama. Rast propusnosti transmisijskih veza za nekoliko redova veličine, uz istodobni superlinearni rast broja mreža oglašenih u globalne tablice usmjeravanja, bili su glavni čimbenici nedostatne propusnosti usmjeritelja temeljenih na tadašnjim mikroprocesorskim platformama opće namjene. Tijekom 90-ih godina prošlog stoljeća predložen je niz algoritama za poboljšanje učinkovitosti programski ostvarenog pretraživanja globalnih tablica usmjeravanja, informacije o kojima Internetski usmjeritelji

razmjenjuju putem protokola Border Gateway Protocol (BGP). Tadašnje tablice usmjeravanja sadržavale su manje od 100.000, dok današnje premašuju 760.000 zapisa, pri čemu njihov broj i dalje nezaustavljivo raste, trenutno dinamikom od oko 50.000 zapisa godišnje. Već na prijelazu stoljeća do tada razvijeni algoritmi za programsko pretraživanje tablica usmjeravanja pokazali su se nedostatnim za praktičnu primjenu u opisanim uvjetima i postupno se zamijenjuju specijaliziranim sklopovljem u novijim generacijama Internetskih usmjernika visoke propusnosti. S druge strane, razvoj sve bržih specijaliziranih sklopovskih arhitektura (engl. applicationspecific integrated circuits, ASIC) za usmjeravanje paketa, zbog izrazito visokih troškova može pratiti svega nekoliko najvećih svjetskih proizvođača komunikacijske opreme. Male kompanije i akademske istraživačke grupe praktički nemaju izgleda za proboj i natjecanje u sve užem krugu takvih proizvođača, čime se koči razvoj inovacija. U praksi se pokazalo da, zbog svojih fiksnih kapaciteta, sklopovske arhitekture Internetskih usmjeritelja imaju kratak eksploatacijski rok trajanja, tipično od svega nekoliko godina. Problem je ilustriran primjerom iz kolovoza 2014. godine kad su zabilježene značajne oscilacije i nedostupnost pojedinih mreža u Internetu zbog rasta globalnih tablica usmjeravanja preko praga od 512 \* 1024 IPv4 zapisa, što je bilo sklopovski uvjetovano ograničenje dijela tadašnjih usmjeritelja. Uz već spomenut visok rizik, dugotrajnost, i cijenu razvoja, povećanje kapaciteta obrade specijaliziranih sklopovskih usmjeritelja ograničeno je visokim razinama potrošnje i disipacije energije. Poseban problem je nefleksibilnost specijaliziranog sklopovlja u smislu prilagodbe modernim trendovima eksploatacije, kao što su virtualizacija mrežnih funkcija (engl. Network Function Virtualization, NFV), i programski definiranih mreža (engl. Software Defined Networking, SDN). Napredak tehnologije generičkih programirljivih logičkih sklopova (Field-Programmable Gate Array -FPGA) omogućio je njihovu praktičnu primjenu u platformama za obradu mrežnog prometa koje imaju bolje mogućnosti prilagodbe novim zahtjevima od usmjeritelja temeljenih na sklopovima ASIC, ali istodobno nude značajno manji kapacitet odnosno propusnost od sklopovskih rješenja. Upravo su spomenuta tehnološka ograničenja postojećih sklopovskih rješenja potaknula autora na istraživanje mogućnosti (ponovne) primjene modernih mikroprocesorskih platformi za brzu obradu paketa u Internetskim usmjeriteljima. U prvom poglavlju se opisuje i trenutni raskorak između zahtjeva za propusnošću današnjih transmisijskih tehnologija (10, 100, 400 Gbit/s) s kapacitetom obrade programski ostvarenih usmjeritelja temeljenih na operacijskim sustavima (OS) opće namjene. Rezultati vlastitih eksperimenata konzistentni su s izvješćima drugih autora koji ukazuju da je ograničenje propusnosti OS-a opće namjene reda veličine jednog milijuna paketa u sekundi (Mpps) po mikroprocesorskoj jezgri, što je dostatno tek za rad pri brzinama do 1 Gbit/s. Kao alternative tradicionalnom pristupu obradi paketa u jezgri OS-a citiraju se novije paradigme programske obrade mrežnog prometa, pri čemu niz autora predlaže i demonstrira značajno poboljšanje propusnosti zaobilaženjem mrežnog stoga OS-a prilikom prihvata i odašiljanja paketa. Međutim, rješenja problema učinkovitog pretraživanja

tablica usmjeravanja do nedavno se i dalje tražilo isključivo kroz delegiranje (engl. offload) na zasebno sklopovlje, npr. jezgre grafičkih procesora, ili raspoređivanjem prometa na više fizičkih računala opće namjene.

Drugo poglavlje ("Programska obrada paketa: sklopovska perspektiva") ispituje ključna svojstva suvremenih tržišno-dominantnih mikroprocesora: paralelizam i hijerarhije predmemorija. Dan je pregled stanja modernih višejezgrenih mikroprocesora opće namjene, gledano kroz prizmu zahtjeva za obradom velike količine međusobno nezavisnih podataka u jedinici vremena, što je svojstveno obradi mrežnog prometa u Internetskim usmjeriteljima, te posebno problemu brzog pretraživanja tablica usmjeravanja. Ističe se problem stagniranja rasta frekvencije radnog takta, koje su od početka 80-ih godina prošlog do prvih godina ovog stoljeća narasle za približno tri reda veličine, od četiri MHz do nešto manje od četiri GHz, što je kroz zadnjih petnaestak godina ostala gornja granica frekvencije radnog takta najbržih komercijalnih mikroprocesora. Istodobno je nastavljen tehnološki razvoj litografskih postupaka u proizvodnji poluvodiča, odnosno gustoće integracije elektroničkih elemenata, da bi i napredak tih tehnoloških procesa počeo pokazivati značajne trendove stagniranja tijekom posljednjih nekoliko godina. Kao temeljni čimbenici zaustavljanja napretka u brzini rada mikroprocesora ističu se povećanje propagacijskih kašnjenja unutar prospojnih puteva između elektroničkih elemenata pri novijim tehnološkim procesima, te posebno velika gustoća snage toplinske disipacije pri radu na visokim frekvencijama takta. Isti tehnološki problemi uvjetuju i teškoće u razvoju novih generacija specijaliziranih integriranih krugova za obradu i usmjeravanje Internetskog prometa, koji su dodatno ekonomski opterećeni visokim troškovima razvoja sklopovlja prolagođenog najnovijim tehnološkim procesima poluvodičke litografije, koje je teško amortizirati kroz relativno male serije u kojima se takvi specijalizirani sklopovi proizvode, za razliku od mikroprocesora opće namjene koji se proizvode masovno i imaju veliko, još uvijek nepresušno tržište. Tako je istaknut primjer dominantnog proizvođača komunikacijske opreme čiji se usmjeritelji najvećeg kapaciteta predviđeni za rad u jezgri Interneta i dalje temelje na specijaliziranom procesoru predstavljenom još 2013. godine, a čija je propusnost za današnje prilike skromnih 280 Mpps. U nastavku poglavlja analiziraju se temeljne značajke modernih mikroprocesorskih platformi opće namjene. To su mogućnost izvođenja više instrukcija u jednom ciklusu takta (engl. instruction-level parallelism / superscalar execution), dinamičko predviđanje grananja (engl. branch Ppediction), dinamički odabir i izvođenje instrukcija izvan programskog slijeda uz zadržavanje semantike slijednog izvođenja (engl. out-of-irder execution), višerazinske hijerarhije predmemorija (engl. caches) kojima se vrijeme slučajnog pristupa približno udvostručuje sa svakom razinom većeg kapaciteta, te glavne memorije velikog kapaciteta s vremenom slučajnog pristupa reda veličine do 100 ns, odnosno od oko 300 ciklusa radnog takta procesorske jezgre. Ispitivanje vremena slučajnog pristupa predmemorija i glavnoj memoriji provedeno je vlastitim jednostavnim programom pokrenutim na nizu računala izgrađenim oko različitih procesora proizvođača Intel i AMD, a opaženi rezultati konzistentni su s vrijednostima objavljenim od strane samih proizvođača. Uslijed stagnacije povećanja brzina izvođenja jedne programske dretve (engl. thread), moderni mikroprocesori sadrže sve više procesorskih jezgri koje dijele zajedničku glavnu memoriju i dio (zadnju razinu) predmemorije. Svaka procesorska jezgra uobičajeno podržava izvođenje do dvije nezavisne programske dretve, s glavnim ciljem iskorištenja sklopovlja u vrijeme dok druga programska dretva na istoj jezgri čeka na dohvat podataka iz predmemorije ili iz glavne memorije. Kroz konkretni eksperiment paralelnog pretraživanja tablica usmjeravanja prikazana je razlika u izvođenju algoritma na fizički odvojenim jezgrama u usporedbi s izvođenjem dvije dretve na jednoj jezgri, koje je manje učinkovito. Na kraju poglavlja iznosi se niz prijedloga za oblikovanje podatkovnih struktura i algoritama kao sinteza vlastitih i opažanja drugih autora, a koje proizlaze iz svojstava današnjih mikroprocesorskih platformi opće namjene. Zbog stagnacije napretka u brzini izvođenja pojedinačnih dretvi (engl. single-thread performance) što je inherentno svim generacijama mikroprocesora uvedenih na tržište tijekom proteklog desetljeća, ističe se nužnost fokusiranja na oblikovanje algoritama i podatkovnih struktura prilagođenih učinkovitom paralelnom izvođenju na više procesorskih jezgri. Zbog velikog raskoraka u brzini slučajnog pristupa predmemoriji i glavnoj memoriji podatkovne strukture nužno je oblikovati tako da zauzimaju što manje memorijskog prostora, kako bi čim većim dijelom i uz što manje istiskivanja (engl. spilling) mogle biti dohvaćane iz predmemorija procesora. Umjesto tradicionale raspršenosti manjih fragmenata podatkovnih struktura po širem adresnom prostoru, organiziranje podatkovnih struktura u kompaktne neprekinute blokove omogućuje konsolidaciju memorijskih stranica (engl. pages) uobičajene veličine od 4 KB u veće cjeline (engl. superpages) koje obuhvaćaju 1 MB do 4 MB linearnog adresnog prostora, što smanjuje potrebu za intervenciju operacijskog sustava u upravljanju sklopovskim translacijskim tablicama (engl. translation lookaside buffers - TLB) virtualne memorije. Korištenja pokazivača koji na današnjim 64-bitnim procesorskim arhitekturama imaju mali omjer korisne informacije i zauzeća prostora treba gdje je moguće zamijeniti indeksiranjem, primjena kojeg osim manjeg zauzeća memorije inherentno potiče organizaciju podataka u kompaktnije, linearne, neraspršene strukture. Podatke koje se većinu vremena čita a rijetko ažurira mogže se dijeliti između više programskih dretvi, ali strukture koje se često ažuriraju potrebno je alocirati u nezavisnim instancama za svaku dretvu, kako bi se smanjila potreba za implicitnim (sklopovskim) i eksplicitnim (programskim) sinkronizacijskim operacijama nad dijeljenim blokovima podataka. Dugo vrijeme slučajnog pristupa podacima u glavnoj memoriji može se dijelom kompenzirati korištenjem procesorskih instrukcija za najavu pristupa (prefetching) kako bi se podaci unaprijed dohvatili u predmemoriju za tijekom izvođenja instrukcija neovisnih o ciljanim podacima.

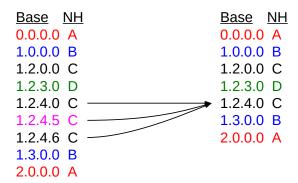

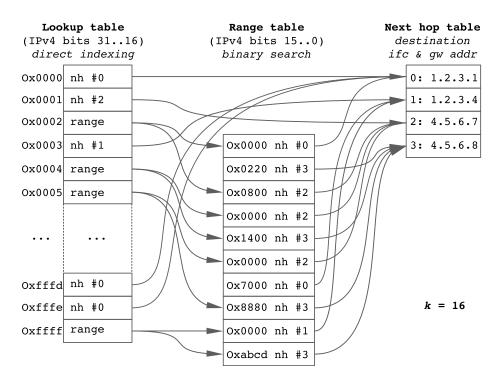

Treće poglavlje ("Direktno / rasponsko pretraživanje najdužih prefiksnih podudaranja") predstavlja temeljna načela koja se nalaze iza ključnog doprinosa, sheme pretraživanja nazvane

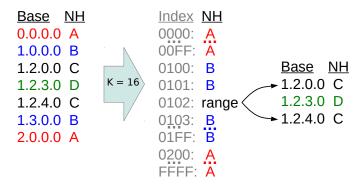

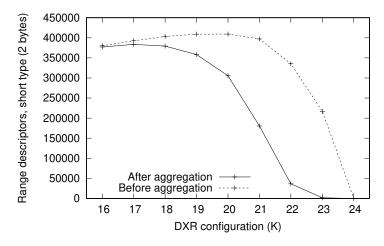

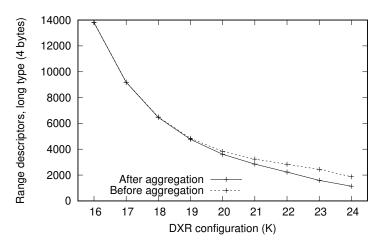

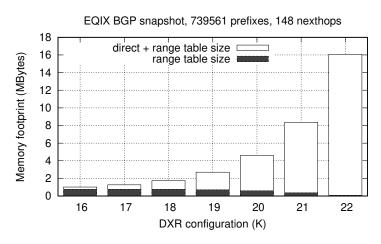

Direct / Range, skraćeno DXR. U uvodnom dijelu poglavlja opisuju se glavne značajke popularnog IPv4 LPM postupka DIR-24-8, razvijenog krajem prošlog stoljeća s ciljem (tada) učinkovite sklopovske izvedbe uz korištenje dediciranih memorijskih modula DRAM, a danas je u širokoj primjeni kao standardni modul odnosno biblioteka u programskim platformama za obradu mrežnog prometa Click i DPDK. Postupak DIR-24-8 se oslanja na dvije pregledne tablice, od kojih se glavna (veća) formira projiciranjem IPv4 prefixa iz izvorne tablice s mrežnim maskama širine do 24 bita na linearno polje veličine 2<sup>24</sup> elemenata. Elementi glavne pregledne tablice sadrže informaciju o usmjeravanju (engl. next hop, NH), ili u slučaju da u izvornoj tablici postoje zapisi s identičnih 24 bita veće težine ali s mrežnom maskom koja zahvaća više od 24 bita, element glavne pokazuje na segment druge (pomoćne) tablice u kojem se indeksiranjem s preostalih 8 bitova traženog ključa pronalazi konačna informacija o usmjeravanju. Opisana podjela odabrana je temeljem razdiobe širina mrežne maske (engl. prefix length) IPv4 zapisa u tablicama usmjeravanja u jezgri Interneta, u kojima su najzastupljenije mrežne maske širine do uključivo 24 bita, dok su širine mrežne maske od 25 bitova i više razmjerno rijetke. LPM pretraživanje u postupku DIR-24-8 je trivijalno, a svodi se na direktno indeksiranje glavne pregledne tablice pomoću 24 bita veće težine traženog IPv4 ključa, te po potrebi dodatnim indeksiranjem pomoćne tablice preostalim bitovima ključa. Međutim, kako pregledne tablice postupka DIR-24-8 svojom veličinom nadilaze kapacitet predmemorija većine mikroprocesora opće namjene, uz upite ključevima disperziranima po cijelom IPv4 adresnom spektru predmemorije gube na učinkovitosti, što je temeljni nedostatak postupka pri paralelnom izvođenju na višejezgrenim mikroprocesorima s dijeljenom glavnom memorijom. U nastavku poglavlja opisuje se koncept transformiranja tablica mrežnih prefixa u uređen slijed susjednih adresnih raspona (engl. ranges), koji obuhvaćaju cijeli IPv4 adresni prostor. Nakon takve transformacije LPM pretraživanje svodi se na trivijalno binarno pretraživanje adresnih raspona. Kako je svaki raspon definiran početnom i završnom 32-bitnom adresom te NH oznakom za koju se u praksi pokazalo da je dovoljno 16 bitova, za svaki zapis o adresnom rasponu dovoljno je 10 byteova, uz pretpostavku da se zapisi pohranjuju slijedno u kontinuirano polje kako bi se isto moglo iteracijski pretraživati. U ovakvoj podatkovnoj strukturi značajan je višak informacije, budući da je početna adresa svakog adresnog raspona uvijek jednaka završnoj adresi prethodnog uvećanoj za jedan. Izostavljanjem završne adrese raspona iz zapisa, koja se može izvesti iz početne adrese slijedećeg, veličina zapisa smanjuje se na 6 byteova. Veličina tablice s adresnim rasponima u najgorem slučaju proporcionalna je broju zapisa u izvornoj tablici, što bi za današnje izvorne tablice usmjeravanja s preko 750.000 IPv4 mreža rezultiralo tablicom raspona s do 1.5 milijun elemenata, ukupne veličine do 9 MByte, za pretraživanje koje bi bilo nužno do 20 iteracijskih koraka, što je neostvarivo u ciljanim vremenskim okvirima od nekoliko desetaka ciklusa procesorskog takta. Zauzeće memorije može se smanjiti podjelom adresnog prostora na  $2^K$  jednakih blokova, te korištenjem početnih K bitova tražene adrese za direktno

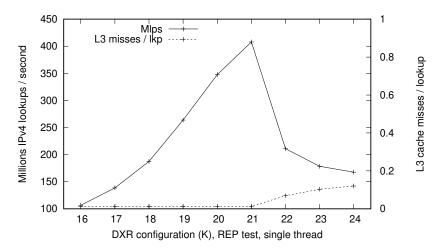

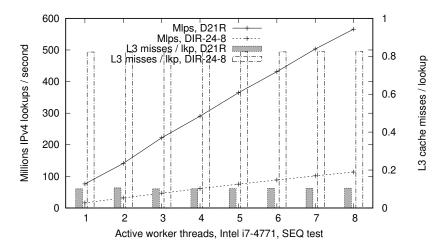

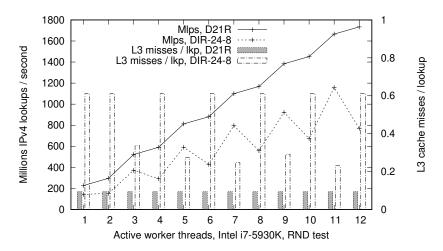

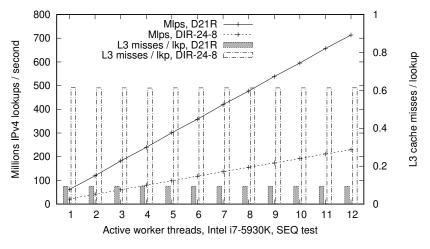

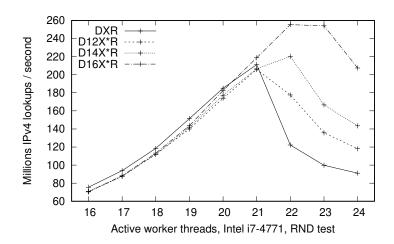

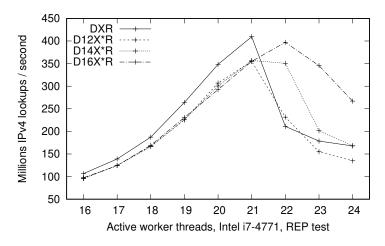

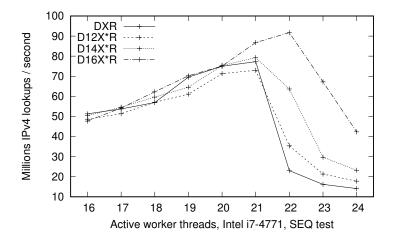

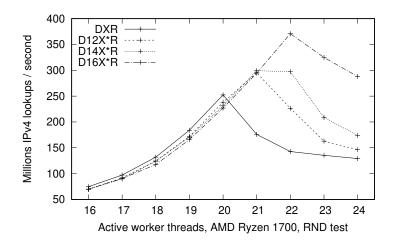

indeksiranje dodatno uvedene pregledne tablice, pri čemu se adresni rasponi razvijaju zasebno za svaki od uniformnih blokova. Uz odabir vrijednosti K veći ili jednak 16, 16 bitova veće težine u zapisima s početnim adresama adresnih raspona postaju suvišni, pa se veličina pojedinog zapisa smanjuje s 6 na 4 bytea. Dodatno optimiranje veličine zapisa može se ostvariti za adresne raspone koji ne proizlaze iz IPv4 mreža s mrežnom maskom širom od 24 bita, te ukoliko mogućih odredišta (next hop) nema više od 256, u kojem slučaju nije potrebno pamtiti 8 bitova najmanje težine početne adrese raspona (uvijek su nula), pa je zauzeće memorije po zapisu moguće sažeti na svega 2 bytea. U nastavku poglavlja opisan je postupak iteracijskog pretraživanja s konkretnom izvedbom u programskom jeziku C. Postupak pretraživanja analizira se iz perspektive organizacije predmemorija modernih mikroprocesora u tzv. retke (engl. lines) veličine 64 bytea, što uz spomenutu linearnu organizaciju zapisa o adresnim rasponima osigurava da se zapisi pri završnim koracima iteracijskog postupka pretraživanja dohvaćaju iz razine predmemorije koja je najbliža procesorskoj jezgri te ima najmanje trajanje dohvata podataka. Slijedi opis i analiza postupka formiranja i ažuriranja preglednih tablica uz korištenje tablice usmjeravanja preuzete iz usmjernika u jezgri Interneta. Kao izvorišna baza (tablica) za pohranu informacija o IPv4 mrežama koristi se već postojeća, provjerena implementacija binarnog stabla sa skraćenim putevima preuzeta iz operacijskog sustava FreeBSD, na temelju koje se formiraju direktna tablica (engl. direct table) i tablica adresnih raspona (engl. range table). Zavisno od odabira vrijednosti parametra K, u rasponu između 16 i 20, postižu se ukupne veličine preglednih tablica između jednog i pet MByte, odnosno od 1.76 do 7.32 bytea po IPv4 mreži u izvorišnoj tablici. Odabirom veće vrijednosti parametra K smanjuje se broj iteracija potrebnih za razriješenje LPM upita, ali se povećava zauzeće memorije te vrijeme potrebno za formiranje preglednih tablica. Analizom tablice adresnih raspona za K veći ili jednak 16, uočena je pojavnost raspona koji imaju identične bitove manje težine i pripadajuće informacije o usmjeravanju, ali su povezani s odvojenim dijelovi IPv4 adresnog prostora, odnosno imaju različite prvih K bitova veće težine. Kako se K bitova veće težine ne pohranjuje u zapisima o adresnim rasponima, nego se razrješuju indeksiranjem prve tablice, opisane identične adresne raspone moguće je objediniti, i time smanjiti zauzeće memorije, što se pokazalo posebno učinkovito pri odabiru parametra K većih od 19. U nastavku poglavlja prikazani su i analizirani rezultati ispitivanja propusnosti algoritma s nizovima slučajno odabranih ključeva. Ispitivana su tri tipska scenarija za različite izvorišne tablice preuzete s usmjernika iz jezgre Interneta, s različitim konfiguracijama parametra K, na nizu različitih računala temeljenim na komercijalno dostupnim mikroprocesorima proizvođača AMD i Intel. U prvom tipskom scenariju svi su slučajno odabrani ispitni ključevi međusobno nezavisni. U drugom tipskom scenariju u ispitnu proceduru umjetno se uvodi međuzavisnost između uzastopnih pretraživanja superponiranjem rezultata prethodnog pretraživanja sa slijedećim slučajno odabranim ključem, čime se u značajnoj mjeri blokira mogućnost mikroprocesorske jezgre za špekulacijskim izvođenjem. U trećem

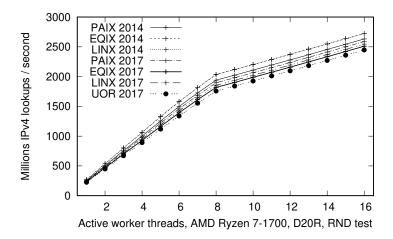

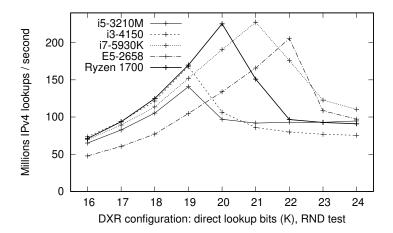

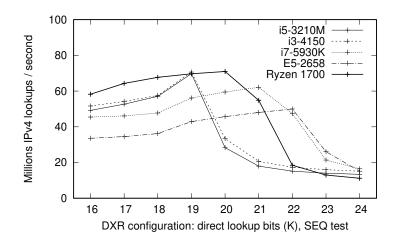

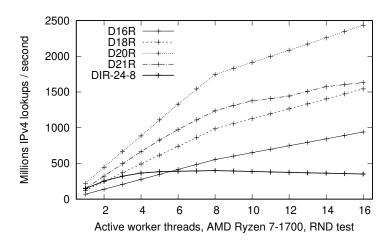

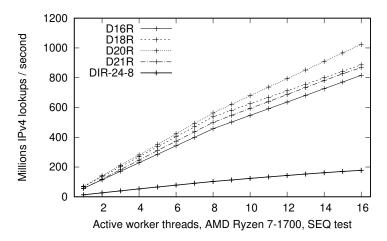

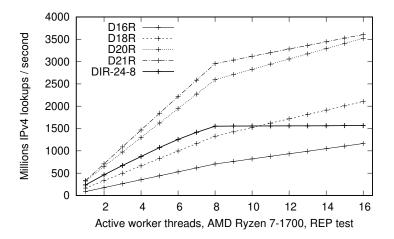

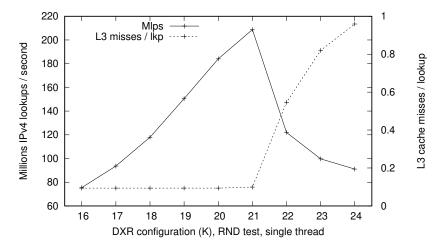

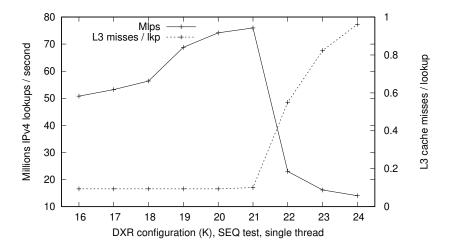

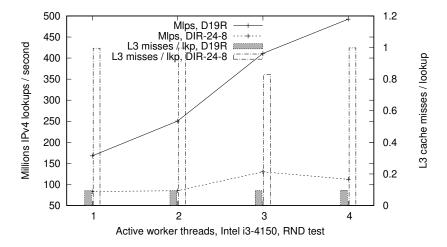

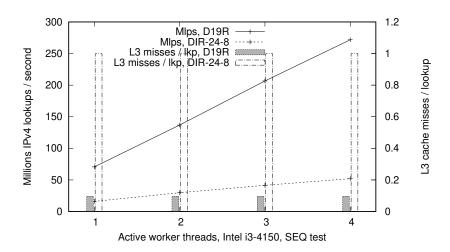

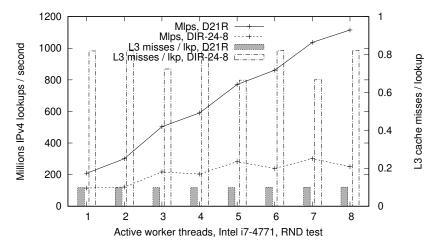

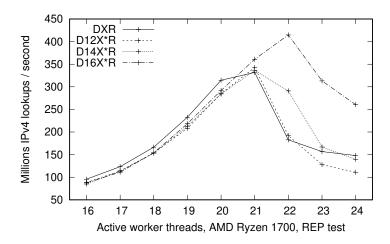

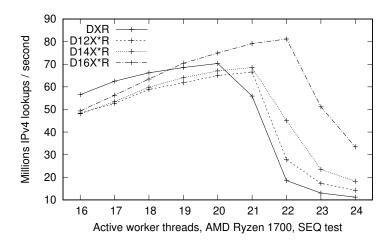

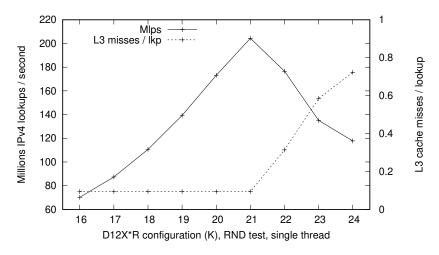

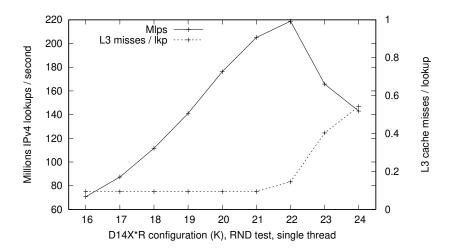

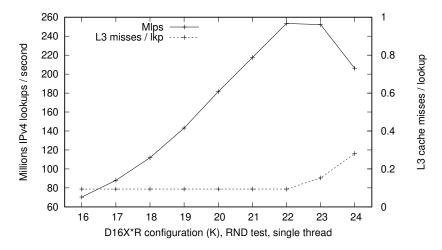

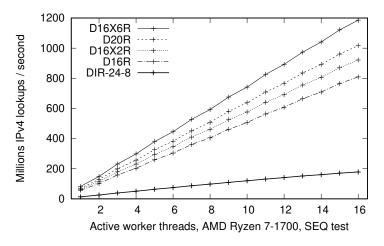

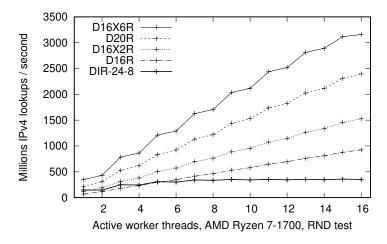

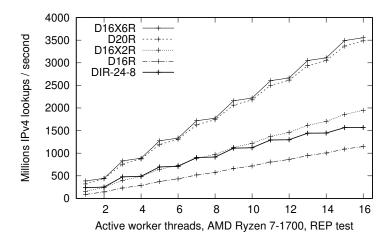

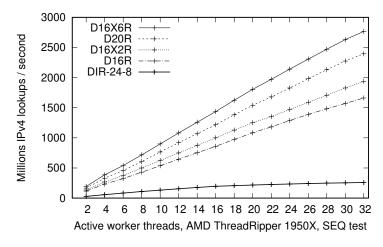

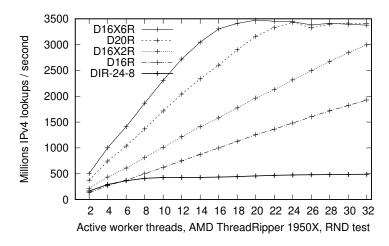

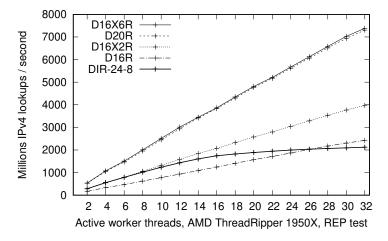

tipskom scenariju za svaki od slučajno odabranih ključeva LPM upit se ponavlja osam puta, s ciljem simuliranja pojave usnopljenosti mrežnih tokova. Rezultati eksperimenata pokazuju da se za prvi tip ispitivanja s nezavisnim slučajno odabranim ključevima najviša propusnost na jednoj procesorskoj jezgri, razina do 230 milijuna upita u sekundi (engl. million lookups per second - Mlps), postiže pri odabiru parametra K između 19 i 22, zavisno od mikroprocesora na kojem se eksperiment provodi, odnosno veličine njegovih predmemorija. U drugom tipskom ispitnom scenariju, s međuzavisnošću između slijednih LPM upita, postižu se propusnosti do 70 Mlps na jednoj procesorskoj jezgri. Pri paralelnom izvođenju algoritma na više procesorskih jezgri postižu se propusnosti do 2490 Mlps na 16-jezgrenom procesoru AMD Ryzen 7-1700. Eksperimenti pokazuju približno linearan rast propusnosti algoritma s raspoređivanjem na više procesorskih jezgri, dok isti eksperiment proveden s algoritmom DIR-24-8 pokazuje stagnaciju i pad ukupne propusnosti pri raspoređivanju na više od šest jezgri, u kojim uvjetima se postiže propusnost od ukupno 430 Mlps, dakle skoro red veličine manje od optimalne konfiguracije algoritma DXR na istom stroju. Poglavlje završava analizom učestalosti promašaja pri dohvatu podataka iz predmemorije (engl. cache miss) temeljem očitanja sklopovskih brojila takvih događaja u mikroprocesoru. Konkretno, za mikroprocesor Intel i7-4771 koji je opremljen s 8 MByte predmemorije zadnje razine (engl. last level cache), broj promašaja pri dohvatu iz predmemorije konstantan je za sve ispitivane konfiguracije algoritma do uključno K=21, za koju je pregledne tablice zauzimaju ukupno 8.35 MByte. Prikazana je usporedna analiza učestalosti promašaja dohvata iz predmemorije za odabrane konfiguracije algoritma DXR i DIR-24-8 u režimu paralelnog izvođenja na više jezgri, iz kojih je vidljva značajno veća učestalost promašaja pri izvođenju LPM pretraživanja algoritmom DIR-24-8, koja doseže razinu od 0.8 do 1 promašaja po LPM pretrazi, zavisno od kapaciteta predmemorije procesora na kojem se provodi ispitivanje. Za optimalno odabrane konfiguracije algoritma DXR bilježe se razine od 0.1 promašaja po LPM pretrazi, koje su neizbježno uvjetovane dohvatom unaprijed pripremljenih slučajno odabranih ključeva iz zasebne tablice. U opisanim mjerenjima promašaja dohvata iz predmemorije zabilježena je propusnost LPM pretraga algoritma DXR u rasponu od približno 1.5 do 5 puta većoj od propusnosti algoritma DIR-24-8.

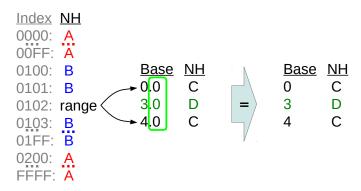

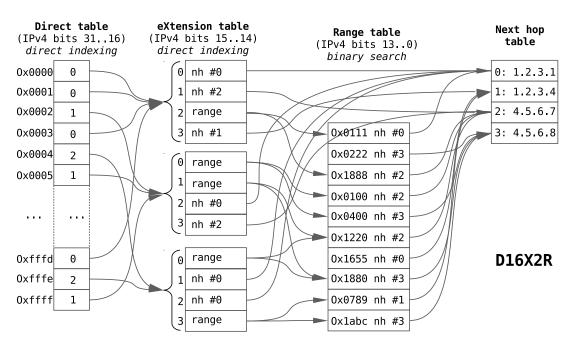

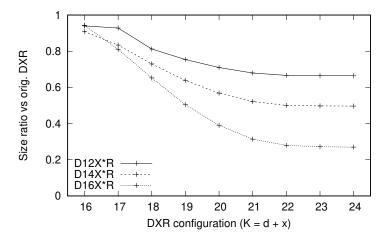

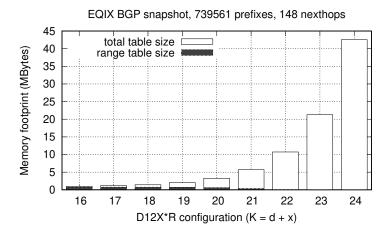

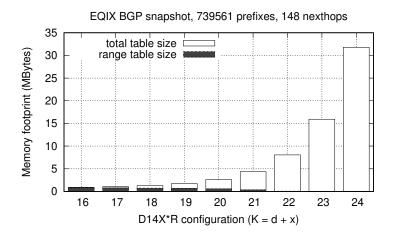

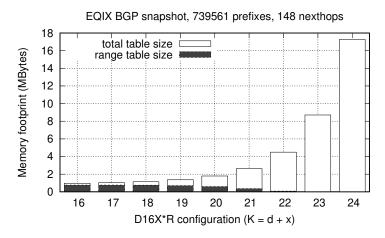

Četvrto poglavlje ("Daljnje vremenske i prostorne optimizacije") opisuje i analizira optimizacije algoritma DXR koje se postižu uvođenjem dodatne tablice, kojom se direktno indeksiranje temeljem prvih K bitova ključa rastavlja u dva koraka. Razdvojene tablice nazvane su direktna (engl. Direct) i proširena (engl. eXtension) tablica. Direktna tablica indeksira se s početnih D bitova ključa, dok se s dodatnih X bitova indeksira odabrani blok u proširenoj tablici, pri čemu je zbroj D+X=K. Uvođenjem druge, proširene tablice, omogućuje se smanjenje zauzeća memorije, pronalaženjem i objedinjavanjem (engl. deduplication) blokova koji pokazuju na iste zapise u tablici adresnih raspona. Postupak objedinjavanja blokova proširene tablice pokazao se posebno učinkovit pri odabiru parametara D=16, te X>3. Konkretno, za

konfiguraciju D = 16, X = 6 postiže se sažimanje memorije od približno 70% u usporedbi s odgovarajućom konfiguracijom K = 22 temeljne inačice algoritma. Gledano iz druge perspektive, uz približno isto zauzeće memorije, inačica algoritma s dvije tablice moći će razriješiti do dva bita ključa više indeksiranjem tablica, prije prelaska na sporiji, iteracijski postupak pretrage tablice adresnih raspona. Skraćenje iteracijskog binarnog pretraživanja odražava se na povećanje propusnosti koja pri izvođenju na jednoj procesorskoj jezgti dosežu do 40% više razine u usporedbi s temeljnom inačicom. Pri paralelnom izvođenju optimiranog algoritma u konfiguraciji D = 16, X = 6 na svim logičkim jezgrama procesora AMD Ryzen-7 1700 postiže se propusnost od 3204 Mlps, u usporedbi s 2490 Mlps koje na istom računalu ostvaruje konfiguracija K = 20 temeljne inačice. Najviša ukupna propusnost od 3491 Mlps ostvarena je pri ispitivanju algoritma na procesoru AMD ThreadRipper 1950X. Spomenute razine propusnosti odnose se na prvi tipski test, uz nezavisne slučajno odabrane ključeve, dok se uz ponavljajuće upite za isti ključ (treći tipski test) na procesoru AMD 1950X postiže ukupna propusnost od 7207 Mlps. Važno svojstvo optimirane inačice algoritma je i značajno manje zauzeće memorije kod tablica usmjeravanja s malim brojem zapisa u usporedbi s temeljnom inačicom. Primjerice, mala tablica usmjeravanja sa samo pet IPv4 mreža i konfiguraciji D = 12, X = 9 preslikat će se u pregledne tablice sa zauzećem memorije od svega 15 Kbyte.

Peto poglavlje ("Integracija u podatkovne staze") opisuje mogućnosti integriranja algoritma DXR u programski ostvarene IPv4 usmjeritelje. Obrazlažu se razlozi odustajanja od početnih napora za ugradnju algoritma DXR u jezgru operacijskog sustava FreeBSD, te odluke da se algoritam implementira u dvije inačice nezavisne od OS-a. Inačica na kojoj su se provela sva ispitivanja opisana u ovom radu implementirana je kao *lookup* modul u popularnoj programskoj platformi za obradu paketa *Click*, pri čemu je najveći dio modula ostvaren u programskom jeziku C++, uz enkapsuliranje komponenti preuzetih iz operacijskog sustava FreeBSD (*radixtree*) u zasebnu klasu. Na temelju te referentne implementacije razvijena je i ispitana samostalna DXR biblioteka ostvarena u ANSI C-u, s ciljem lakše integracije u aplikacije neovisne o platformi *Click*. Korištenjem spomenute biblioteke i platforme za brzo dohvaćanje i odašiljanje paketa *netmap* konstruirana je ispitna aplikacija koja je pokazala mogućnost proslijeđivanja paketa uz provođenje LPM pretraga bez gubitaka pri brzini od 10 Gbit/s, odnosno 14.88 Mpps, korištenjem samo jedne mikroprocesorske jezgre. Ispitivanja rada pri višim brzinama prijenosa nije bilo moguće provesti tijekom izrade ovog rada uslijed nedostatka odgovarajuće opreme, odnosno mrežnih kartica.

Šesto poglavlje ("Pregled literature") daje kritički osvrt na stanje istraživanja u području teme doktorskog rada i objavljene rezultate drugih istraživača, s naglaskom na evoluciju LPM algoritma namijenjenih izvođenju na mikroprocesorskim platformama opće namjene, nakon čega slijede završne napomene u sedmom poglavlju.

Zaključno, znanstveni doprinos disertacije uključuje novu klasu algoritama i kompaktnih

podatkovnih struktura za brzo programsko pretraživanje usmjerivačkih informacija za protokol IPv4; poboljšanja učinkovitosti podatkovnih staza u programskoj komutaciji paketa boljim iskorištavanjem prostornih i vremenskih mogućnosti paralelne obrade na procesorima opće namjene; te izvedbu dvije parametrizirane verzije sheme pretraživanja DXR, kao programske biblioteke i kao komponente za korištenje u modularnom programskom usmjeritelju Click, uz empirijsku provjeru ispravnosti njihovoga rada.

Ključne riječi: internetski usmjeritelji, pretraživanje najdužih prefiksnih podudaranja, programska komutacija paketa

# **Contents**

| 1. | Intro                                | oduction                                        | 1  |  |  |  |  |  |  |  |  |  |  |

|----|--------------------------------------|-------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|

|    | 1.1.                                 | Background and motivation                       | 1  |  |  |  |  |  |  |  |  |  |  |

|    | 1.2.                                 | Thesis overview                                 | 4  |  |  |  |  |  |  |  |  |  |  |

|    | 1.3.                                 | Summary                                         | 5  |  |  |  |  |  |  |  |  |  |  |

| 2. | Pack                                 | xet processing software: a hardware perspective | 6  |  |  |  |  |  |  |  |  |  |  |

|    | 2.1.                                 | Moore's law demise                              | 7  |  |  |  |  |  |  |  |  |  |  |

|    | 2.2.                                 | Parallelism in contemporary CPUs                | 8  |  |  |  |  |  |  |  |  |  |  |

|    | 2.3.                                 | Memory hierarchies and latencies                | 10 |  |  |  |  |  |  |  |  |  |  |

|    | 2.4.                                 | Recommendations                                 | 12 |  |  |  |  |  |  |  |  |  |  |

| 3. | Dire                                 | Direct-Rrange longest prefix matching lookups   |    |  |  |  |  |  |  |  |  |  |  |

|    | 3.1.                                 | Prefix expansion into address ranges            | 16 |  |  |  |  |  |  |  |  |  |  |

|    | 3.2.                                 | Building the search data structure              | 17 |  |  |  |  |  |  |  |  |  |  |

|    | 3.3.                                 | Saving space and time                           | 19 |  |  |  |  |  |  |  |  |  |  |

|    | 3.4.                                 | Lookup algorithm                                | 22 |  |  |  |  |  |  |  |  |  |  |

|    | 3.5.                                 | Updating                                        | 26 |  |  |  |  |  |  |  |  |  |  |

|    | 3.6.                                 | Performance evaluation                          | 30 |  |  |  |  |  |  |  |  |  |  |

| 4. | Further space and time optimizations |                                                 |    |  |  |  |  |  |  |  |  |  |  |

|    | 4.1.                                 | Data structures, deduplication                  | 42 |  |  |  |  |  |  |  |  |  |  |

|    | 4.2.                                 | Lookup algorithm                                | 44 |  |  |  |  |  |  |  |  |  |  |

|    | 4.3.                                 | Performance evaluation                          | 45 |  |  |  |  |  |  |  |  |  |  |

| 5. | Data                                 | path integration                                | 52 |  |  |  |  |  |  |  |  |  |  |

|    | 5.1.                                 | FreeBSD kernel                                  | 52 |  |  |  |  |  |  |  |  |  |  |

|    | 5.2.                                 | The Click Modular Router                        | 54 |  |  |  |  |  |  |  |  |  |  |

|    | 5.3.                                 | User-space Packet Processing Library            | 55 |  |  |  |  |  |  |  |  |  |  |

|    | 5 4                                  | Future directions                               | 56 |  |  |  |  |  |  |  |  |  |  |

| 6.  | Related work    | . 57 |

|-----|-----------------|------|

| 7.  | Conclusion      | . 62 |

| Bil | bliography      | . 64 |

| Ac  | ronyms          | . 72 |

| Cu  | ırriculum Vitae | . 73 |

| Ži  | votopis         | . 76 |

# Chapter 1

## Introduction

## 1.1 Background and motivation

In the early 21st century, the availability of ubiquitous, affordable, reasonably fast and reliable packet-switched communication on a global scale, in a network known as the Internet, became simply taken for granted, just like running water, electrical energy distribution, or mass transportation, became infrastructural norms over the course of the previous century. The entire human society is becoming intrinsically dependent on packet-switched communication.

The increases in global Internet traffic volume [1], the pressure on the global routing system [2] [3] [4], and particularly the advances in transmission link speeds, have been among the major driving forces behind the development and evolution of the global Internet infrastructure, particularly its core. The perpetual race between the raising demands at improving the speed, scalability, power consumption, cost effectiveness, and hardware lifecycle duration in the Internet core has been driving the engineering response and led to the introduction, adoption, as well as demise of numerous concepts and packet switching technologies over the past two decades.

In the aftermath of extensive research, development, and operational deployment on a historically unparalleled scale, backed by a multi-trillion dollar per year industry, a widely held public perception is that packet switching in the Internet is a solved technical problem, i.e., something which "just works", yet the reality can be different from popular beliefs. For example, on August 12, 2014, due to forwarding tables of certain widely deployed routers being limited to supporting no more than 512K IPv4 prefixes, significant world-wide Internet connectivity outages were observed when the number of prefixes announced in the global routing system exceeded the aforementioned threshold [5] [6]. Approximately a year prior to that event, on the launch date of its latest flagship core router, a dominant network equipment vendor admitted that the product's interface cards based on a newly designed, state-of-the-art application-

specific integrated circuits (ASIC) would not be capable of line rate packet forwarding, but had to be designed oversubscribed at a greater than 1:2 ratio in terms of packets per second forwarding rate capacity [7], far from the full line rate minimum-sized packet forwarding capacity which previously stood among the paramount requirements and performance metrics for core Internet routers since the turn of the century. Even as link speeds progress from 100 to 200 and 400 Gbit/s, the high complexity, risks and enormous costs of developing new ASIC routing hardware are reflected in the difficulty of the industry to deliver improved chips. For example, the Cisco's flagship nPower X1 ASIC from 2013 still has no publicly announced successor at the time of this writing (early 2019).

Software based routers have lost the performance parity with their hardware-based counterparts more than two decades ago. The technological advances in link speeds, in particular 10 Gbit/s Ethernet becoming ubiquitous in recent years, made the already known performance limitations of the traditional network stacks in general purpose operating system (OS) kernels more pronounced. As an example, while a general-purpose OS may successfully forward minimumsized packets at line rates or emulate networked environments operating in 1 Gbit/s range in real time, it typically struggles with faster link speeds. The measurements the author performed on the FreeBSD operating system (the reference platform used in the experiments throughout this thesis) revealed that its packet forwarding throughput is currently limited to around 1 million packets per second (Mpps) per central processing unit (CPU) core, and that it saturates at even lower speeds if packet filtering is applied, while exhibiting relatively poor scaling properties when running on multicore CPUs. This is consistent with our earlier experiments [8] [9], while others, e.g., Bianco et al. [10]; Bolla et. al. [11]; Brouer [12] observed similar levels of performance in different operating systems. Since a single 10 Gbit/s Ethernet packet flow may require processing up to 14.88 Mpps unidirectionally, the widening performance gap between link speeds and capabilities of contemporary operating systems becomes more palpable.

Advances [13] [14] [15] in improving packet processing efficiency in software have demonstrated that modern commodity CPUs and network interface cards may indeed be capable of absorbing and forwarding packet flows at around 10 Gbit/s line rates. The key to achieving higher throughputs seems to be in blending together several techniques aimed at lowering the effective per-packet handling overhead: processing packets in batches, by carefully engineered data prefetching, minimizing lock contentions, and bypassing the OS network stack altogether. Nevertheless, packet forwarding based on IPv4 (and IPv6) routing lookups is still deemed too demanding a task for a purely software implementation above 10 Gbit/s speeds with large routing tables characteristic for today's Internet exchange points, so the spectrum of different proposals ranges from offloading routing lookups to general-purpose (GP) graphical processing unit (GPU) hardware [14] to distributing the load among multiple physical machines [13] for increased aggregate throughputs.

Examining IP routers [16] as a particular category of packet processors, especially in software based implementations, reveals that IPv4 (and subsequently IPv6) next hop lookups have become a major performance bottleneck already more than two decades ago. The Classless Interdomain Routing (CIDR) [2] principle mandates that an Internet router must select a next hop associated with the most specific network prefix matching the each packet's destination address, i.e., perform a longest prefix matching (LPM) search in the entire routing database. In routers participating in global routing information exchange via the Border Gateway Protocol (BGP) [17] the size of the routing (forwarding) database as of today exceeds 760,000 prefixes, and the prefix count growth shows no signs of abating. As early routing database structures and algorithms (such as [18]) were designed to balance lookup throughput and database updating efficiency, they could not cope with the explosive growth of both BGP table sizes and increasing link speeds. In late 1990s, following a few proposals for more efficient routing lookups in software, such as [19] [20], which soon become impractical due to swift increases in BGP table sizes, both the research community as well as the network equipment industry shifted their focus to hardware-based routing lookup schemes and implementations, a trend which continued up to the present time.

While hardware-based routing lookup methods, for example [21] [22], have solved the performance issues in the past and continue to be applied successfully in various flavors in modern high-performance Internet routers, they generally exhibit several significant shortcomings. First, hardware-based lookup implementations must balance the room for future growth in routing table sizes and link speeds within constrained power (current consumption) and thermal (heat dissipation) envelopes. Moreover, such implementations are generally prohibitively expensive and thus reserved only for carrier-grade Internet routers. And finally, hardware-based routing lookup solutions lack the flexibility which is called for in the emerging virtualization and software defined networking (SDN) [23] scenarios and applications. As a consequence, experimentation and innovation in high-speed routing has gradually become constrained in the realm of only a small and closed circle of network equipment vendors who can afford to develop and build ASIC required for the job. Recent advances in field-programmable gate array (FPGA) integrated circuit (IC) densities and speeds has led to proposals [24] which are moving experimentation with network processing in hardware again closer within the reach of the academic research community and smaller companies, but still at more than an order of magnitude lower speeds as compared to top of the line commercial routers.

This thesis revisits the capabilities and limitations of modern commodity microprocessors for routing lookup applications by proposing a class of efficient longest prefix matching schemes, and subjecting them to a thorough empirical performance evaluation. The practical result is a polyvalent implementation, embodied both as a C library, and as a lookup element in the Click [25] modular router, validated for correctness of operation by comparing the lookups

against the proven (yet slow) PATRICIA trie variant [18] borrowed from the FreeBSD OS, using real-life, full-view BGP snapshots obtained from various open Internet exchange points. The proposed class of schemes outperform other common software IPv4 LPM implementations, particularly when running on multi-core commodity CPUs, where near linear scaling in lookup throughput gains can be observed. The small memory footprint of the proposed lookup structures makes them particularly suitable for both network virtualization scenarios, and for scenarios where cascaded lookups in multiple databases may be required on a single packet forwarding or real-time traffic analysis datapath.

### 1.2 Thesis overview

The thesis is organized as follows:

The second chapter examines the key properties of contemporary mainstream microprocessors with emphasis on the widening access speed gaps across memory cache hierarchies, and attempts to establish guidelines for data structure and access pattern design aimed at extracting the most of the performance potential from the abundance of execution cores and symmetric multithreading support available in modern CPUs.

The third chapter introduces the Direct-eXtend-Range (DXR) LPM lookup scheme, presents its fundamental principles of operation, motivates the design choices, and discusses implementation tradeoffs. That chapter is based on and contains revised material from the author's initial work [26] as well as from the more recent paper [27].

The fourth chapter discusses further optimization options, which include tradeoffs between memory footprint reduction through data deduplication at the expense of an additional search step, along with implementational microoptimizations which aim at further compensation of memory access latencies in a single instruction stream through batching and prefetching. The impact of the optimizations is dissected through performance analysis under a set of different operating conditions, which also includes a comparison of DXR with other routing lookup schemes.

The fifth chapter discusses the possibilities for DXR's application in data processing datapaths.

Chapter six describes the related work in the field, followed by concluding remarks presented in the seventh chapter.

## 1.3 Summary

The contributions of this thesis include:

- A new class of algorithms and compact data structures for high-speed IPv4 routing lookups in software;

- Practical implementations of two parametrizable DXR lookup scheme variants, as readyto-use software libraries or Click elements, and their empirical validation for correctness of operation;

- A thorough analysis of lookup throughput of various DXR configurations running on diverse commodity CPUs;

- Improvements in efficiency of software packet processing datapaths by extracting more performance from spatial and temporal parallel processing capabilities of general-purpose CPUs.

# Chapter 2

# Packet processing software: a hardware perspective

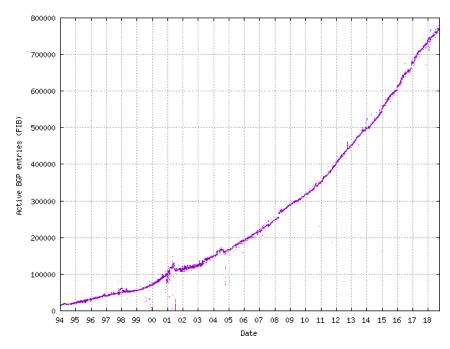

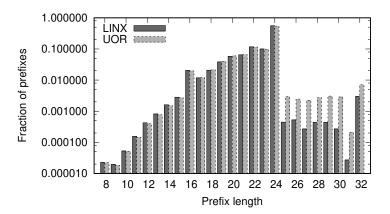

Internet router vendors had to work hard to start introducing 100 Gbit/s interfaces to the market, yet providing sufficient routing lookup throughput remains among the major challenges in designing router interface cards for even higher speeds (200, 400 Gbit/s and above). To forward minimum-sized IPv4 packets at 400 Gbit/s Ethernet line speed, a core Internet router must perform 579 million routing lookups per second (Mlps) in a database which today consists of approximately 760,000 network prefixes [28] and is continually growing, as shown in Figure 2.1. This requirement is more than four times higher than the capacity of a dedicated, state-of-the-art router ASIC from a dominant vendor, which is reportedly limited to 140 Mlps of unidirectional packet forwarding, or 280 Mlps bidirectional [7].

The evolution of routing ASICs is bounded not only by technological challenges in contemporary silicon design and power dissipation management issues at peak operating conditions, but also by the long, complex and risky development cycles, as well as prohibitively high cost of access to advanced silicon manufacturing processes, which permits only a handful of core router vendors to invest in the increasingly expensive design efforts. Consequently, smaller companies and especially academia are faced with a practically impenetrable barrier of entry to innovation in the field of high-performance router design, which negatively impacts the pace of further technological advances.

Compared to software-based routers, a significant drawback of routing ASICs is their relative inflexibility, which becomes more pronounced as network operators embrace various levels of routing function virtualization, and as the ability to quickly respond to unpredictable malicious threats and security challenges is becoming vital to real-world network operations.

A considerable interest has therefore arisen in (re)exploring the feasibility of utilizing generalpurpose CPUs in the forwarding path of high-performance routers, a concept which has been all but abandoned around two decades ago, as it was deemed by far too slow for the rapid increases

**Figure 2.1:** The growth of the global IPv4 BGP routing table as of 09/2018. The current trend indicates an annual growth of approximately 50,000 prefixes. Source: BGP Routing Table Analysis Reports [28]

in transmission rates. However, compared to their counterparts from 15 years ago, contemporary multi-core general-purpose CPUs offer a significantly improved performance potential, which an increasing number of recent proposals [29] [30] [31] [26] aim to leverage to offer routing lookup throughputs which rival or exceed the performance of dedicated router ASICs.

The rest of this chapter focuses on key architectural aspects of contemporary commodity CPUs, aimed at identifying both the potential for efficient resolving of queries in large routing databases, as well as identifying pitfalls which should be avoided when designing data structures and the accompanying lookup algorithms.

## 2.1 Moore's law demise

For the past five decades, the semiconductor technology has been improving at a pace which enabled transistors per area density to roughly double every two years, a rule of thumb which has been colloquially known as the Moore's law [32]. Today's top-of-the-line CPUs are being produced with transistor geometries which are only 14 nm or 12 nm accross. However, as the manufacturers are having a hard time to further shrink the semiconductor process node, there's a widespread consensus that the already faltering Moore's law is about to halt in the near future [33].

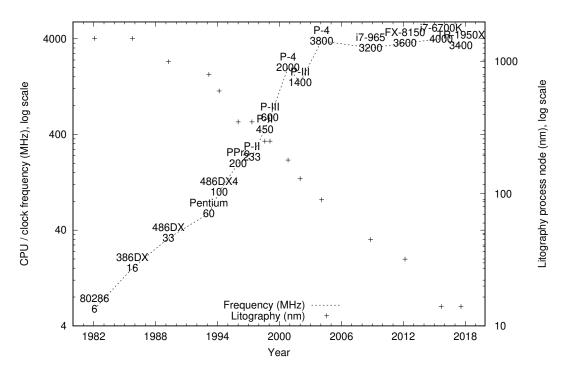

As visible in Figure 2.2, even with manufacturing processes considered mature by today's standards, steady increases in microprocessor clock frequencies characteristic for the past century already hit the ceiling more than a decade ago at around 3.5 GHz [34].

**Figure 2.2:** Evolution of commodity CPU clock frequencies. Manufacturing process geometry is indicated as crosses vertically aligned to each processor, ranging from 1500 nm in 1982 down to 14 nm node which was first introduced in 2015. Sources: Intel and AMD online product sheets.

Reductions in transistor sizes of more than two orders of magnitude (from 180 nm to 14 nm) over the past decade and a half yielded only a two-fold improvement in processor speeds (from 2 GHz to 4 GHz) due to numerous factors, including wire propagation delays starting to dominate timing budgets at tiny process geometries, ever increasing static leakage currents, enormous dynamic power dissipation per area which became increasingly difficult to manage, timing uncertainties in clock distribution trees, etc. [35].

The same set of technological problems is making advances in ASIC performance just as difficult as with the CPUs. However, the microprocessor industry has so far kept itself ahead of the ASIC world by at least one process technology node, due to the economies of scale which permitted CPU vendors to pour more money in the adoption of newer silicon manufacturing processes, to introduce more advanced products faster to the market, and to compensate for lower yields when moving to finer process geometries.

## 2.2 Parallelism in contemporary CPUs

Faced with the inability to continue leveraging clock frequency increases for extracting more performance, CPU designers shifted their focus to less rewarding areas and concepts, such as reducing branch penalties by shortening execution pipelines, increasing cache sizes, extracting more single-stream instruction-level parallelism (ILP) by increasing the number of parallel

functional units, introducing advanced memory prefetch and branch prediction units etc.

However, the most notable differentiator between contemporary lower-end, low-power, embeddable CPUs, and their general-purpose counterparts which power today's laptops, workstations and datacenters, is the ability of the later to speculatively execute instructions far beyond of unresolved data dependencies, a technique known as out-of-order instruction scheduling and execution (OoO). Combined with the abundance of memory load / store buffers found in modern CPUs [36], OoO is the key mechanism which offers an effective compensation for a dramatic mismatch between CPU clock frequencies and slow main memory access times, provided that data access patterns are designed, and the programs are written and compiled in a manner which permits speculative execution deep into an instruction stream, i.e., without excessive data interdependencies. Nevertheless, it was established early on that ILP and OoO have firm limits, which may vary widely depending on the workload type and effectiveness of compiler optimizations, but in general for integer applications can be expected to rarely exceed the range between two and three instructions per cycle (IPC) [37].

The recent series of discoveries revealing a whole class of security vulnerabilities in contemporary CPU hardware, which elaborate various side-channel exploits of speculative execution hardware mechanisms [38] [39] [40], prompted responses from CPU vendors which in one form or another disabled or crippled certain speculative execution hardware blocks in attempts to prevent, or at least minimize, the possibility of data leakages to unauthorized applications. It is therefore reasonable to expect that further advances in single-thread computing performance, i.e., in ILP, which have been bound to speculative execution techniques and machinery, will remain marginal if not negative in the foreseeable future.

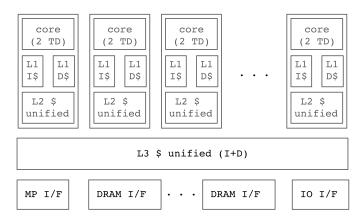

Realizing that microarchitectural innovations are likely to yield only incremental improvements in effective single-thread performance, approximately a decade and a half ago the whole CPU industry shifted towards integrating multiple processing cores en masse on a single silicon die. Therefore, as shown in Figure 2.3, a modern general-purpose processor consists of several execution cores sharing usually three levels of cache hierarchy, along with external memory controller(s), peripheral interfaces, interrupt routing and multiprocessing synchronization units, among other subsystems.

Each physical execution core typically appears as two virtual cores (threads) to the operating system or application software, although the virtual cores share the same execution units in various time-division schemes, all aimed at finding some useful work to do in times of pipeline stalls due to excessive memory access latencies. Cache blocks closer to execution cores are smaller in size but provide faster response to data access requests. The largest, third level (L3) cache, depicted as a single unit in Figure 2.3, in practice usually comprises multiple smaller blocks bonded together via a high-speed interconnect, which may be of ring, point-to-point, or some other topology, the choice of which varies among CPU vendors and their product

**Figure 2.3:** A simplified structural diagram of a typical general-purpose contemporary microprocessor, comprising multiple execution cores, a hierarchy of cache memories, and external interfaces. First-level (L1) instruction (I\$) and data (D\$) caches are separated. Second (L2) and third (L3) caches are unified.

lines [41]. Throughout the memory hierarchy, the main unit of work in hardware interconnects and synchronization machinery is a cache line, an aligned array of  $2^N$  bytes, where the industry appears to have settled on 64 byte blocks as the line size.

Adding more and more cores, regardless whether on a single CPU die or in various multidie / multi-chip topologies, is far from a trivial endeavor, given that all processing cores in

general-purpose computing systems must have the ability to access the whole system's main

memory using an uniform addressing scheme, a concept colloquially known as symmetric multiprocessing (SMP). As the number of computing cores rise, the more challenging it becomes

to efficiently maintain cache coherency and synchronization throughout the memory hierarchy,

which itself gains further complexity by partitioning execution cores among separate silicon

dies, each typically with its own (local) memory controller, in topologies known as non-uniform

memory access (NUMA) [41].

## 2.3 Memory hierarchies and latencies

In contrast to increases by several orders of magnitude in microprocessor clock frequencies, as well as both cache sizes and speeds, which took place over the past four decades, contemporary dynamic random access memory (DRAM) has roughly the same access latencies as their ancient predecessors, at around 50 ns. Effective random access latency as observed from a software thread is somewhat higher, as each request and the corresponding data has to pass through all levels of cache hierarchy which further adds up to the total delay [42].

Memory access latencies of several contemporary microprocessors were characterized using a trivial program which populates a large memory pool with random data and then accesses it inside a timing loop in a way which makes each subsequent memory access dependent on the previous one, thus preventing out-of-order execution mechanics from pipelining or inter-

**Table 2.1:** Characterization of microprocessor cache hierarchies and access latencies. The results are in line with data put forth in Intel's reference manual [36], which estimates L1, L2 and L3 cache latencies at 4, 11 and approx. 34 cycles respectively. The AMD ThreadRipper 1950X CPU includes two silicon dies in a single package, and exhibits increased DRAM latency when accessing physical memory on a die adjacent to the one where the test program was executing, so two DRAM latencies are reported, "local" and "far".

|                    |      |         |       |      | Level 1 Cache |     |      | el 2 Cac | he  | Level 3 Cache |         |      | DRAM    |       |

|--------------------|------|---------|-------|------|---------------|-----|------|----------|-----|---------------|---------|------|---------|-------|

|                    |      | Cores / | Clock | Size | Size Latency  |     | Size | Latency  |     | Size          | Latency |      | Latency |       |

| Processor          | Year | Threads | GHz   | KB   | cycles        | ns  | KB   | cycles   | ns  | KB            | cycles  | ns   | cycles  | ns    |

| Intel i5-3210M     | 2012 | 2/4     | 2.5   | 32   | 7             | 2.9 | 256  | 13       | 5.3 | 3072          | 24      | 9.7  | 214     | 85.8  |

| Intel i3-4150      | 2014 | 2/4     | 3.5   | 32   | 9             | 2.6 | 256  | 16       | 4.6 | 3072          | 35      | 10.1 | 243     | 69.6  |

| Intel i7-4771      | 2013 | 4/8     | 3.5   | 32   | 9             | 2.6 | 256  | 16       | 4.6 | 8192          | 38      | 10.9 | 260     | 74.3  |

| Intel i7-5930K     | 2014 | 6 / 12  | 3.5   | 32   | 9             | 2.6 | 256  | 15       | 4.3 | 15360         | 51      | 14.6 | 263     | 75.2  |

| Intel E5-2658      | 2013 | 10 / 20 | 2.4   | 32   | 9             | 3.8 | 256  | 16       | 6.7 | 25600         | 46      | 19.2 | 237     | 98.8  |

| AMD R7-1700        | 2017 | 8 / 16  | 3.4   | 32   | 10            | 3.0 | 512  | 21       | 6.2 | 2 * 8192      | 43      | 12.7 | 352     | 103.8 |

| AMD TR-1950X local | 2018 | 16 / 32 | 3.4   | 32   | 8             | 2.4 | 512  | 14       | 4.2 | 4 * 8192      | 46      | 13.6 | 296     | 87.3  |

| AMD TR-1950X far   | 2018 | 16 / 32 | 3.4   | 32   | 8             | 2.4 | 512  | 14       | 4.2 | 4 * 8192      | 46      | 13.6 | 452     | 133.2 |

leaving multiple memory accesses. The offset from the previous memory address is alternating from positive to negative, which in addition to randomness harvested from previous reads is aimed at preventing the hardware prefetch units from predicting the location(s) of next memory access(es), initiating such reads speculatively, and thereby compensating for a portion of the effective access latency. The results, presented in table 2.1, indicate that on all tested platforms a DRAM read access would cause a software thread to stall for around 250 clock cycles or at least 70 ns, whichever is longer, unless the CPU's execution scheduler would be able to find instructions not depending on the data in flight from the DRAM and execute those instructions out-of-order. The measurements further show that consistently across all observed platforms each cache level has access latencies approximately double of its counterpart closer to the CPU core, and that DRAM access latency is nearly an order of magnitude longer (slower) than a last-level cache hit.

The physical external memory is inherently partitioned into uniform banks (typically 8 internal banks per chip for modern double data rate (DDR) DRAM memory). The banks can be accessed in an interleaved manner, i.e., while one bank is blocked due to access latency, data can be written to or read from another bank on the same memory chip. A memory controller typically uses an interleaved addressing mapping scheme in order to scatter contiguous data blocks over multiple banks, in an attempt to permit multiple threads, or multiple out-of-order requests from a single thread, to make progress while one bank is blocked. Similarly, consumer-grade microprocessors offer multiple (typically two to four) independent physical memory channels, which can be configured for (again) interleaved addressing scheme, permitting further parallelism or better compensation for lengthy random access cycles. The details of low-level memory interleaving machinery have been traditionally opaque to the operating

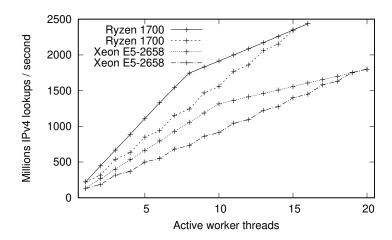

**Figure 2.4:** The effects of scheduling routing lookup worker threads on virtual SMT cores. In the first experiment, for each of the two microprocessors (AMD Ryzen, Intel Xeon) the workload was scheduled on idle physical cores until all became busy, followed by scheduling a second thread with identical workload on each simultaneous multi-threading (SMT) core, leaving a pronounced "knee" in aggregate throughput increase for the second half of worker threads. In the second experiment, identical worker threads were scheduled sequentially in pairs on idle cores, which can be observed as staircase-like throughput increases.

system or application level programs.

Modern CPU cores include resources for multiple (typically two) SMT hardware threads to share the same execution infrastructure utilizing an opaque time-division scheduling scheme, which permits the core to remain utilized in situations when a single thread can not make further progress while waiting for data to arrive from higher levels of cache hierarchy or from external DRAM [43]. The extent to which such a scheduling scheme can make use of otherwise idle CPU cycles, is both hardware and workload dependent. SMT does not come for free, as it typically mandates partitioning L1 caches in two smaller and independent logical blocks, which unavoidably negatively impacts single-thread performance.

As an illustration, the impact of scheduling threads to SMT virtual cores can be observed in Figure 2.4. In the specific experiments presented here, scheduling a second worker thread on a single physical core yielded an increase in table lookup throughput of around 40%, compared to nearly linear scaling (99.7% increase) when the second thread would be scheduled on a separate and otherwise idle physical core.

## 2.4 Recommendations

Extracting performance from modern microprocessors calls for careful design of data structures and the accompanying algorithms and access patterns, which have to be closely matched to the underlying physical machine structures. A set of guidelines is summarized here based on aforementioned properties and limitations of contemporary microprocessors, based on observations

obtained from the experiments described in later chapters, as well as backed by reports from other authors in the field.

- Single-thread performance (ILP) on general-purpose computing platforms is stagnating and is unlikely to further improve in the foreseeable future, therefore significant advances in processing performance may be obtained only by designing data structures and algorithms which are suitable for scalable parallel execution on multiple computing cores.

- DRAM random access latency is the major processing performance obstacle in most packet processing applications, which becomes more pronounced with concurrent access from multiple execution cores as congestions form in memory controller blocks [42].

Hence, keeping both shared and thread-local data working sets as small as possible helps to minimize data spilling from higher levels of cache hierarchies to the lower ones, or to the main memory.

- Sharing of read-only, or read-mostly data between execution cores improves L3 cache effectiveness compared to maintaining a separate copy of data for each core (but not necessarily on NUMA topologies). However, multiple threads should avoid sharing the same cache lines with frequent write patterns, as this will trigger excessive synchronization traffic and incur high access latencies until cache synchronization operations complete [44] [45].

- Keeping the data structures small helps not only to achieve high data cache utilization, but permits consolidation and promotion of smaller (4K) memory pages into virtual memory (VM) objects of bigger size (1M to 4M) which are often called superpages, provided the structures may be organized in a contiguous block of memory. Utilization of superpages may significantly reduce the occurrence of translation lookaside buffer (TLB) spills and refills and thus improve performance [46].

- In cases when location of data which will be required within a short timeframe can be computed in advance, the CPU can be instructed to start fetching such data while other unrelated computations take place, thus preempting excessive memory load stalls. The technique should be used with care as data prefetched too far in advance may be displaced from the buffers / cache by the time it is actually needed, effectively doubling the required traffic throughout the cache hierarchy [45] [15].

- Branches hurt performance, especially those dependent on data which has to arrive from main memory. Branch predictors in modern CPUs may be reasonably accurate for a broad range of general-purpose workloads, thus permitting for speculative execution far ahead of unresolved data dependencies. Nevertheless, when dealing with unpredictable data, such as streams of random keys in LPM applications, the value of branch predictors diminishes. Hence, if branches are unavoidable, the data they depend upon should be already in L1 caches.

- With the general-purpose computing industry converging to 64-bit CPU architectures, the lavish use of pointers should be revisited. The problem with pointers is two-fold. First, being 8 bytes wide, pointers carry little useful information for the amount of memory they consume, and often significantly contribute to the large footprint of data structures based on their excessive use. And second, use of pointers promotes scattering of data structures over broad spans of memory addresses, which may exacerbate data access stalls, as random access latencies to main memory are measured in hundreds of wasted CPU cycles. Replacing pointers with (smaller) indices in linear arrays may significantly reduce memory footprints. Today's CPUs provide efficient bit manipulation instructions which make it feasible to instantly extract smaller bit groups (such as array indices) from naturally (power-of-two) aligned fundamental data types, so attempts should be made to compactly encode data, even if that requires unnatural splits inside 16, 32 or 64-bit words.

- Relying on memory access requests to complete within a fixed timeframe is no longer a practical goal on moder CPUs, because memory subsystem latencies cannot be guaranteed to be bounded as the increasing number of cores compete for the shared main memory. Cache synchronization and coherency mechanisms may further interfere with introducing additional delays, and structural competition between SMT contexts for shared execution units on a single CPU core adds more variance to the problem. Last but not least, packet processing systems will typically operate under significant direct memory access (DMA) load originating from network interface card (NIC)s. Therefore, latency variations must be offset by introducing sizeable queues between hardware and software components of packet processing datapaths.

# Chapter 3

# Direct-Rrange longest prefix matching lookups

The author's interest in improving the performance of software packet datapaths originates from his earlier work on network stack virtualization in the FreeBSD OS kernel [47], and subsequent collaboration on control and data plane integration between the eXtensible Open Router Platform (XORP) [48] and Click [25] platforms.